Cs 1110 Ch 4-1 Combinational Logic. ° Introduction Logic circuits for digital systems may be:...

-

Upload

jayden-romero -

Category

Documents

-

view

217 -

download

2

Transcript of Cs 1110 Ch 4-1 Combinational Logic. ° Introduction Logic circuits for digital systems may be:...

Cs 1110

Ch 4-1

Combinational Logic

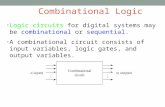

° Introduction

Logic circuits for digital systems may be:

°2

combinational sequentialOR

A combinational circuit consists of logic gates; whose outputsat anytime are determined from only the present combinationof inputs.

A Sequential circuits contain memory elements ; the outputs are a function of the current inputs and the state of the memory elements the outputs also depend on past inputs

A combinational circuits

°4

°Specific functions

°Adders, subtractors, comparators, decoders, encoders, and multiplexers

Combinational circuits Output Input

° Need to formulate circuits from problem descriptions1. Determine number of inputs and outputs

2. Determine truth table format

3. Determine K-map

4. Determine minimal SOP

5. Determine Gate draw Implementations>

o There may be multiple outputs per designo Solve each output separately

Design Procedure:

° Addition and subtraction of binary data is fundamental• Need to determine hardware implementation

° Represent inputs and outputs• Inputs: single bit values, carry in

• Outputs: Sum, Carry

° Hardware features• Create a single-bit adder and chain together

Binary Adders and Subtractors

Half Adder

C A B S 0 0 0 1 A 0 B 0

S 0

C 1

0 0 0 00 1 1 01 0 1 01 1 0 1

Dec Binary 1 1+1 +1 2 10

° Add two binary numbers• A0 , B0 -> single bit inputs

• S0 -> single bit sum

• C1 -> carry out

• Half-Adder (HA), a 2-input bit-wise addition functional block.

Circuit diagram

Block diagram

C S

Functional Block: Half Adder

° A 2-input, 1-bit width binary adder that performs the following computations:

° A half adder adds two bits to produce a two-bit sum

° The sum is expressed as a sum bit , S and a carry bit, C

° The half adder can be specified as a truth table for S and C

X 0 0 1 1

+ Y + 0 + 1 + 0 + 1

C S 0 0 0 1 0 1 1 0

X Y C S

0 0 0 0

0 1 0 1

1 0 0 1

1 1 1 0

Logic Simplification: Half Adder

° The K-Map for S, C is:

° This is a pretty trivial map!By inspection:

° and

° These equations lead to several implementations.

Y

X

0 1

321

1

S Y

X

0 1

32 1

C

)YX()YX(S

YXYXYXS

)(C

YXC

)YX(

Implementations: Half Adder

° The most common half adder implementation is: (e)

YXCYXS

XY

C

S

Full Adder

° Full adder includes carry in Ci

Note: 2 out-puts

• Full-Adder (FA), a 3-input bit-wise addition functional block.

Note: 3 inputs

Full Adder

0 0 0 0 00 0 1 1 00 1 0 1 00 1 1 0 11 0 0 1 01 0 1 0 11 1 0 0 11 1 1 1 1

Ci Ai Bi Si Ci+1

1 1

1 1

Ci

AiBi00 01 11 10

0

1

Si

° Full adder includes carry in Ci

° Notice interesting pattern in Karnaugh map.

Note: 3 inputs

Full Adder

0 0 0 0 00 0 1 1 00 1 0 1 00 1 1 0 11 0 0 1 01 0 1 0 11 1 0 0 11 1 1 1 1

Ci Ai Bi Si Ci+1 Si=!Ci!AiBi+!CiAi!Bi+Ci!Ai!Bi +CiAiBi

° Full adder includes carry in Ci

° Alternative to XOR implementation

° Reduce and/or representations into XORs

Si= !Ci !Ai Bi+ !Ci Ai!Bi+ Ci !Ai !Bi+ Ci Ai Bi

Si= !Ci !AiBi + Ai!Bi) + Ci(!Ai!Bi + AiBi)

Si= !Ci(AiBi) + Ci !(Ai Bi)

Si = Ci (Ai Bi)

Full Adder

0 0 0 0 00 0 1 1 00 1 0 1 00 1 1 0 11 0 0 1 01 0 1 0 11 1 0 0 11 1 1 1 1

Ci Ai Bi Si Ci+1

1

1 11

Ci

AiBi00 01 11 10

0

1

Ci+1

° Now consider implementation of carry out

° Two outputs per full adder bit (Ci+1, Si)

Note: 3 inputs

Full Adder

0 0 0 0 00 0 1 1 00 1 0 1 00 1 1 0 11 0 0 1 01 0 1 0 11 1 0 0 11 1 1 1 1

Ci Ai Bi Si Ci+1 Ci

AiBi00 01 11 10

0

1

1

1 11

Ci+1Ci+1 = AiBi+ CiBi + CiAi

° Now consider implementation of carry out

° Minimize circuit for carry out - Ci+1

Full Adder

Ci+1 = Ai Bi + Ci!AiBi + CiAi!Bi

Ci+1 = AiBi+ Ci (!Ai Bi + Ai !Bi)

Ci+1 = AiBi + Ci (Ai Bi)

Recall:

Si = Ci (Ai Bi)

Ci+1 = Ai Bi + Ci (Ai Bi)

Full Adder

A

B

S

C

C i+1

i

i

i

i

Si = Ci (Ai Bi)

Half-adder Half-adder

Ci+1 = AiBi + Ci (Ai Bi)

° Full adder made of several half adders

Full Adder

half-adder

half-adderA

B

i

i

C i

C i+1

S i

S

C

C

A full adder can be made fromtwo half adders (plus an OR gate).

° Hardware repetition simplifies hardware design

Full Adder

Full Adder

A B

C C

S

i i

i+1 i

i

Block Diagram

° Putting it all together • Single-bit full adder

• Common piece of computer hardware

Full Adder

Full Adder

A B

C C

S

i i

i+1 i

i

° How to design circuit to add 2 bits? 2-bit Adder

° 4 bit? 4- bit Adder

° 8 bit ? 8-bit Adder

° By using chain of one-bit Adder??!!

4-Bit Adder

Full Adder

A B

0 C

S

0 0

1

0

Full Adder

A B

C

S

1 1

2

1

Full Adder

A B

C

S

2 2

3

2

Full Adder

A B

C S

3 3

4 3

C 1 1 1 0A 0 1 0 1B 0 1 1 1S 1 1 0 0

° Chain single-bit adders together.

° What does this do to delay?

° The approach is call ripple-carry addition• Can be slow for large designs