Count #0’s Count #1’s Logic Decision 2 CLK CLKout DATAin DATAout

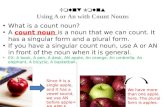

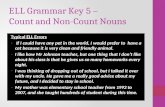

-

Upload

darren-cobb -

Category

Documents

-

view

222 -

download

0

description

Transcript of Count #0’s Count #1’s Logic Decision 2 CLK CLKout DATAin DATAout

Count #0’s

Count #1’s

0

Logic DecisionXNOR (MSBDatadisparity,

MSBChanneldisparity)

2

CLK

CLK

CLK

RST

+

-

+

+

-

+

+

+

-

DATAinDATAout

DC

BalFlag

DataDisparity

ChannelDisparity

-

CLK

CLK CLKout

CLK

Count #1’sBits (15:8)

Count #1’sBits (7:0)

0

Logic DecisionXNOR (MSBDatadisparity,

MSBChanneldisparity)

2

RST

+

-

+

+

+

+

+

-

DATAinDATAout

DC

BalFlag

DataDisparity

ChannelDisparity

CLK

CLK CLKout

CLK

Data Disparity

Clock 0

Clock 3

Clock 4

Xn: 14 bits Xn_m: 14 bits Xn_m_k: 14 bits Xn_2m_k: 14 bits

TrapzFilt

MSearch

25bitsMax

Sign

RESETEvent

Clock 0

Clock 1

Clock 2

Xn: 14 bits Xn_m: 14 bits Xn_m_k: 14 bits Xn_2m_k: 14 bits

Clock 3

+ + + +

+ -

+ +

Trapezoidal Filter

Xn: 14 bits Xn_m: 14 bits Xn_m_k: 14 bits Xn_2m_k: 14 bits

+ + + +

+ -

+ +

Trapezoidal Filter and Pole zero correction

+ +

+ +

<<1

+ +

New_prod(32:14) =>New_prod / 16k

New_result

New_sum

New_sum * 2

New_sum * 3

sum2sum1

sub1

Result = siNo pole zero correction

ResetSi(32) == ‘1’

Xn: 14 bits Xn_m: 14 bits Xn_m_k: 14 bits Xn_2m_k: 14 bits

+ + + +

+ -

+ +

Trapezoidal Filter and Pole zero correction

+ +

+ +

<<1

+ +

New_prod(32:14) =>New_prod / 16k

New_result

New_sum

New_sum * 2

New_sum * 3

sum2sum1

sub1

Result = siNo pole zero correction

Reset LED

ADC data: 14 bits

Energy

LED

clk

clk

clkclk

clk

clk

clkThreshold

AboveTh

AboveTh

AN

D

LED

- +

To Energy max/min search

Reset

DoubleCorrelationEnable

PZEnable

Xn: 14 bits Xn_m: 14 bits Xn_m_k: 14 bits Xn_2m_k: 14 bits

+ + + +

+ -

+ +

Trapezoidal Filter and Prog.Pole zero correction

+ +

x x

+ +

New_prod(32:14) =>New_prod / 16k

New_result

New_sum

Prog PZ multiplier

sum2sum1

sub1

Result = siNo pole zero correction

Reset

ADC data: 14 bits

LED

LED

clk

clk

clkclk

clk

clk

clkThreshold

AboveTh

-

To Energy max/min search

PZEnable

Pipe 1

Pipe 2

Pipe 4

Xn: 15 bits

Xn-1: 15 bits

Sum: 16 bits

Yn: 17 bits

Xn-2: 15 bits + 1 0

+

+

Pipe 3

ADC

ADC

ADC

ADC

ADC

ADC

ADC

ADC

ADC

ADC

FIFO DAC

VMEFPGA

FBBuffer

SD Chip

FIFOInterface

DACControl

VMEControl

Front BusLogic

MasterLogic

MasterLogicEnable

C.C. LED

C.C. PileUp

Main FPGA requirements

EN

Channels

ADC

ADC

ADC

ADC

ADC

ADC

ADC

ADC

ADC

ADC

CH. 9

CH. 8

CH. 7

CH. 6

CH. 5

CH. 4

CH. 3

CH. 2

CH. 1

CH. 0

FIFO DAC

VMEFPGA

FBBuffer

SD Chip

FIFOInterface

DACControl

VMEControl

Front BusLogic

MasterLogic

MasterLogicEnable

CC_TS,CC_Energy

C.C. PileUpm CC_LED,CC_energy_ready

Main FPGA

EN

LEDs Aux. IO

TapDelay1

TapDelay2

TapDelay3

TapDelay4

Circular Buffer

LED

CFDEnergy

Pre-Buffer

ProcCore

ADC Data Debug Data

CFD

Data

EN

ER

GY

circular buffer40us

7 BRAM

8BRAM * 10 ch = 801Multiplier * 10ch = 10Total is 90 out of 96.

Header Memory

Validate

HeaderMemory1

HeaderMemory16

PREBUFFERDATA...

TimingSM

HeaderSM

PackageSM

PileUpCounter

WaitCounter

CircularBuffer

CFD2CFD1Energy

CFDTimeStamp

LEDTimeStamp

Trigger/Validate

EnHM

SizeCBStartAddr

PreBufferAdderss

Timer

HMWrSel

DataSel HMRdSel

CircBufferAddress

EN

EN

LED_TSFBLED_TS

Raw Data

Board_IDTimeOutFlag

CFD_TS

FB_LED

TimeOutFlag

PreBufferHeader

MemorySM

Data_out

Header Memory (HM) Diagram

ChannelSM

FIFO

TimerStartExternalValidationWait

ValidateStatus

Header DataRead_ENWrite_EN

ExternalValidation

Program IDLE Trigger

WaitCounter

Timing State Machine

TapDelayValid &Enable = 1 &LED or ValidateProgramFlag

ProgramACK

IDLE

Sliding

WaitCounter

PrebufferStartPosition

Header Memory State Machine

ComputeDone &NoPileUP

SlidingDone

BoardId

Size

LED_TS

LED_TS

LED_TS

ENERGY

CFD_TS

CFD_TS

CFD_TS

CFD1

CFD1

CFD2

CFD2

Package State Machine

IDLE

RawData

BoardId

Size

LED_TS

LED_TS

LED_TS

ENERGY

CFD_TS

CFD_TS

CFD_TS

CFD1

CFD1

CFD2

CFD2

PreBufferReady &ExternalValidation &ValidateHMValid

LoadCBStarAddress

Sliding

Channel 0 Channel 1

Stay untildone

Channel 6 Channel 5

Channel 8

Channel 9 Channel 2

Channel 3

Channel 7 Channel 4

9 Bit Counter

Stay untildone

Stay untildone

Stay untildone

Stay untildone

Stay untildone

Stay untildone

Stay untildone

Stay untildone

Stay untildone

Start/done Start/done

Start/done

Start/done

Start/done

Start/doneStart/done

Start/done

Start/done

Start/done

FIFO Interface

MasterFB

Front BusSM

FB_Data(9:0)FB_Address(7:0)

FB_Data_Dir

Front Bus Logic Diagram (slave)

Channels

SlaveRegisters

LED_Status(9:0)

Time Stamp(47:0)

Other_Status(9:0)

SLAVE_Board_ID

FB_Strobe*

FB_Data_EN

HM_Validate, FB_Sync

HM_Address(3:0)

Clear Hit Pattern

When the Master Logic is disabled the signals are Just routed to the outside buffers.

Slave Header data package

TS_FB_LED

FB_RNW

VMEControl

FB_LED

Slave Header Data

Front Bus State Machine Diagram (slave)

IDLE SETDATA

WAIT WAIT

ReceivedValidCmd(FB_cmd = Valid &FB_add = 000 or MyAdd)

READ

ReceivedValidCmd(FB_cmd = Valid &FB_add = 000 or MyAdd)

Master Write Master Read

50MHz

IDLE

Comp TS

Set Flag

SetCalChargeInject

LatchStatus

100MHz

FB_CLK

FB_ADD

FB_RNW

FB_ACTIVE*

FB_DATA Master Data Slave Data

WRITE READ

Front Bus Timing Diagram

DATA

CLK

Address

Strobe*

ZZ Data

XX

ZZ

Address XX

RNW XX XX

Write Operation

DATA

CLK

Address

Strobe*

ZZ Data

XX

ZZ

Address XX

RNW XX XX

Read Operation

VMEFPGA

VMESM

VME Diagram

Channels

CLK50

Latch VME Signals

ProgFlag

ProgFlag

ProgFlag

ProgFlag

ProgFlag

ProgFlag

ProgFlag

ProgFlag

ProgFlag

ProgFlag

ReadRegFlag

ReadRegFlag

ReadRegFlag

ReadRegFlag

ReadRegFlag

ReadRegFlag

ReadRegFlag

ReadRegFlag

ReadRegFlag

ReadRegFlag

FIFO

VME State Machine

DACChips

Front BusSM

DATA

DAQ Diagram

VMEInterface

Channels

CH0

CH9

Constantvalue

DAQ State Machines

IDLE Prog

IDLE VerifyAddr

WriteData

RegAddr = MyAddr

ProgFlag = ‘0’

RegFlag = ‘0’

DataReceived = ‘1’

SDChip

SDTx Logic

SDRx Logic

MasteSlaveLogic

Master Logic Diagram

Main Logic

TTCL

DataStatusCtrl. Sig.

Fast DataCH0

CC LED& PileUP Flags

CC LED & PileUp

FrontBus

FBDriver

FBSlave

VMEControl

Master Logic Registers

SDChip

Master Logic Header

ch’s

SDChip

SDTx Logic

SDRx Logic

Serdes Logic Diagram

Main Logic

TTCL

DataStatusCtrl. Sig.

Fast DataCH9

CC LED

CC PileUp

Front BusLow Level

SM

FB_CTRL_Dir

Master Front Bus Diagram

MasterMain Logic

CommandCommand_FLagCommand_ACKBusy

FBBuffer

FB_Data(9:0)FB_Address(1:0)

FB_Data_Dir

FB_cmd(3:0)

FB_Data_EN

FB_CTRL_EN

FB_CTRL_Dir

SlaveFB

FB_Data(9:0)FB_Address(1:0)

FB_Data_Dir

FB_cmd(3:0)

FB_Data_EN

FB_CTRL_EN

Registers

Enabled

Front BusHigh Level

Logic

NewCmdAddressRNWBusy

Data_INData_Out

Enabled

RegDataProgFlagProgAddrProgData

RegAddress1

ProgAck

Reg0

RegN

.

.

.

RegAddress1

RegData

Front Bus State Machine Diagram (master)

IDLE

SetGet Slow Data 0

Cmd Register

100MHz

Get Slow Data 0

SetGet Slow Data 1

Get Slow Data 1

DISABLED

Write TS 0

Write TS 1

Write TS 1b

Write TS 2

Write TS 3

Write TS 4

Write TS 5

Write TS 6

Write TS 7

Write TS 8

Write TS 9

Write TS 10

FBLL_Busy

FBLL_Busy

FBLL_Busy

FBLL_Busy

FBLL_Busy

SetGet Slow Data 2

Get Slow Data 2

SetGet Slow Data 3

Get Slow Data 3

FBLL_Busy

FBLL_Busy

FBLL_Busy

FBLL_Busy

Wait

FBLL_Busy

Write DebugData

Wait

Read DebugData

Wait data

Save Data

Save Last hitpattern

ClearHitPattern

Front Bus Low Level State Machine Diagram (master)

IDLE SETCTRL

SETDATA WAIT1

NewCmdFlag & RNW

SETCTRL

NewCmdFlag & RNW*

50MHz

WAIT2LatchData

WAIT

DISABLED

FB_SM Low Level Flags

CLK

RS

T

Sen

dCm

d

Don

e

BusyFlagARST ARSTSET

CLK

RS

T

New

Cm

d

New

Cm

dAck

NewCommandFlagARST ARSTSET

Send Command

IDLE Send Command

ReceiveBoard 1

Master Logic Front Bus State Machine

ReceiveBoard 0

Stay untilDone or Timeout

Stay untilDone orTimeout

Stay untilDone orTimeout

Stay untilDone

ReceiveBoard 3

Send Command

Stay untilDone orTimeout

Stay untilDone orTimeout

ReceiveBoard 2

SendCommand

Stay untilDone orTimeout

Stay untilDone orTimeout

SDChip

RX State Machine

FIFOMaster

Main Logic

SD Rx Diagram

DCBalLogic Cor.

CommandRebuilder(demux)

SD_RX_Data_IN

SD_RX_CLK50

SD_Lock SD_EN

Data

SE_Lock

Package_error

Command_Ready (‘1’ if cmd != Null)

DATA 5x16

DemuxAddress

DataRdy

BRAM

SD_RPDWN

Disabled Debug

Trigger

Trigger

Trigger

Trigger

Trigger

Trigger

Trigger

SD Rx State Machine

Reset

SD_EN& SD_Lock_N*

Slow Data

Internal

Wait Sync

Trigger

Spare

Internal

Async

Spare

Auxiliary

Spare

Spare

Package Error

End-of-cicle

Word 1

Word 2

Word 3

Word 4

Word 0

Disabled

Reset

WaitSyncCmd

ReS

yncC

md

SD_EN& SD_Lock_N*

ReadSyncCmd

NewCmdReady

NewCmdReady

SD_RX_SM Flags

CLK

RS

T

Pac

kage

Err

or

Rea

dSyn

cCm

d

ReSyncCmdARST ARSTSET

SDChip Bram

AddressIn

SDMain Logic

SD Rx Snap Shot Memory

Address out

Data

CLK50

CLKRST

DataReadEN

BusyEmptyStartRec

Busy

SD_RX_ Snap Shot Memory Flags

CLK

RS

T

Sta

rtRec

ordi

ng

Add

ress

In

BusyARST ARSTSET

CLK

RS

T

Add

ress

Out

Bus

y

EmptySET ARSTSET

SDChip

TX State Machine

DC Bal.

SDMain Logic

SD Tx Diagram

Add Fast Data

DataPack.

Data

CLK50

SD_EN

Package_Ready

DATA 13x8

DemuxAddress

Fast DataCH9

CC LEDCC PileUp

XTAL_ID

BufferCnt

DCBalWord

Error

GrayCounterDataFlag

Counter_EN / Counter restPackage Latched

SD_TPDWN_N

SD_Sync

SD_Lock_N

Reset Buffer Cnt

CLKRST

CLK50_IN

Disabled Buffer_Count

Spare

Hit Pattern A

Hit Pattern B

Hit Pattern C

Hit Pattern D

Hit Pattern E

TS (Low byte)

SD Tx State Machine

Reset

DataPack_TX_EN

DC Bal. word/Spare

CCEnergy (HB)

XTAL_ID.

TS (High byte)

CCEnergy (LB)

DC Bal. word/Spare

DC Bal. word

DC Bal. word

DC Bal. word

DC Bal. word

DC Bal. word

DC Bal. word

DataPack_TX_EN*

DataPack_TX_EN*

IDLE

Reset

LatchData

ResetBufferCntSYNC

SD_EN

Lock_N

PackageReady&HasPackage*

SD_TX_SM Flags C

LK

RS

T

Pac

kage

Rea

dy

Pac

kage

Sen

t

HasPackageARST ARSTSET

CLK

RS

T

P P

ResetBufferCntsigARST ARSTSET

CLK

RS

T

P P

LatchDataSigARST ARSTSET

DataPack_TX_ENLock_N

SD_EN

TSMemory

MainState Machine

FIFOTS TriggerDecision

DataPack.

Counter

Counter_EN

WR

_EN

FBControl

DataCmd

TS

Comparator

Readout_cm

d

TSState Machine

Status

RD_EN

Com

p_EN

FIFO_Empty

Counter_RST

Readout_cm

d

Counter

SD RX

SD TX

DataReady

Main Logic Diagram

Command ready

CC TS

Comp. SystemInSyncFlag

TTCL TS

VMEInterface

TS Data

TSMemory

Block

Processing Core

FIFOTS TriggerDecision

WR

_EN

FBControl

Data_TX

Cmd

TS

Readout_cmd

RD_EN

FIFO_Empty

SD RX

SD TX

DataReady

Main Logic Diagram

Command ready

CC TS

SyncComp

SystemInSyncFlag

TTCL TS

VMEInterface

TS D

ata

Data_Rx

Com

pTypeLatch CC TS

TS & CompType

HM Position

Latch

CC

_LE

DLo

ad T

S

CC

_LE

D

Ene

rgyR

eady

TS D

ata

Fast Flags & Status byte

Energy and TS_LB and TS_HB

TSMemory

Registers MainState Machine

FIFOTS TriggerDecision

WR

_EN

Com

pType+TS

Comparator(48bits)

TSState MachineStatus

Empty#ofMemoccupied

RD_EN

StartC

omp

FIFO_Empty

Com

pResult

Counter(4 bits)

Time stamp memory Block Diagram

ReadoutCmd

TS

CompType

Com

pDone

Add1ClearCounter

AckReadoutCmd

FIFO_DataOut

T155, T15A, T1A5,T255,T25A,T2A5

TS, HMPos, Load

Erase Count

HM_Pos

Time stamp State Machine

Add 1

Compare

Readoutcmd

IDLE

Reset

StartComp

FifoEmpty* and TSMemoryEmpty*

Remove FIFOData

Count = “1111”

Count != “1111” CompResul*

CompResul

CompDone*

StartComp

Ack*

FifoEmpty* and TSMemoryEmpty

Empty_1

LoadLogic

Time stamp memory Registers Diagram

EraseLogic

TS Mem.Cell 0

TS Mem.Cell 15

TS Mem.Cell 1

.

.

.

HM_Pos_Rd

TS_Dataout

TS_Datain

Load

HM_Pos_LD

Erase

LD_0

LD_1

LD_15

ER_0

ER_1

ER_15

TS_MemoryEmptyEmpty_15

Empty_0

HM_Empty

Register

Time stamp memory Cell Diagram

Timer

TS_DataoutTS_Datain

Load

Erase

TS_MemoryEmptyEmptyFlag

TimeoutFlag

TimeoutFlag EmptyFlag

EmptyFlag

Time stamp memory Comparator (48 bits)

CompB ≥ A

TS_Datain

TS_MemoryEmpty

+

+

CLK

B A

CompType

T1A5T15AT155

TS_FIFO

TS_FIFO

CLK

CLK

CLK

CompB ≥ A

-

+

CLK

A B

T2A5T25AT255

SMCompDone

StartComp

Time stamp memory Comparator (48 bits)

CompB ≥ A

TS_Datain

TS_MemoryEmpty

+

+B A

CompType

T1A5T15AT155

TS_FIFO

TS_FIFO

CompB ≥ A

-

+A B

T2A5T25AT255

CompDone

StartComp

Vcc

Time stamp memory Comparator (48 bits)

Comp 1

Comp 2

Comp 3

Reset

IDLE

CompDone

StartComp

StartComp

StartComp*

StartComp*

TSMemory

Block

State Machine

FIFOTS Trigger Decision

FBControl

SD RX

SD TX

Processing Core

CC TS

VMEInterface

Registers

Registers

Registers

Registers

Processing Core Main State Machine

Reset

IDLE

Readout cmdto FB

Get Hit Pattern FB

Evaluate cmdf. SD_Rx

Syncinternal

Load Data into Fifointernal

FrontEndCalInjectTo FB

Demand slow data

Has Datato SD_Tx

Wtrite TS to SlavesTo SD

Check Slaves syncTo SD

TS_MemBlorReadoutFlag

GetHitPatternFlag

SD_RXCmdFlag

CommandId:Sync

CommandId:TriggerDec

CommandId:FrontEndCalInject

Latch statusTo FB

CommandId:Demand Slow data

CommandId:LatchStatus

Imperative Sync

Front end reset

Processing Core Read Register State Machine

IDLE

Read Reg.f.VME

VMEReadFlag

Processing Core Flags

CLK

RS

T

Ser

Des

RE

adD

ata

Rea

dout

Cm

dSD

TX

HasDataFlagARST ARSTSET

CLK

RS

T

Sys

tem

InS

yncF

lag

P

ErrorFlagARST ARSTSET

CLK

RS

T

CC

_LE

D

Has

Dat

aFla

g

GetSlowDataFlagARST ARSTSET

CLK

RS

T

Sys

tem

InS

yncF

lag

??

SyncFlagARST ARSTSET

HM

_TS

Rea

dout

cmd

SD

TXR

eado

utcm

d

ReadoutCmdlFlagARST ARSTSET

Processing Core Register structure

Write logic (21 registers)VME

CLK

RS

T

VM

EP

rogF

lag

VM

Esi

gnal

s

VME

Write logic (11 registers)FB

CLK

RS

T

FBP

rogF

lag

FBsi

gnal

s

FB

Read LogicVME

VM

ER

egFl

ag

VM

Esi

gnal

s

Read RegisterDataRegisters

32x32bits

CLK

RS

T

IDLE

Reset

Package_Ready

SD Main State Machine

Exec_cmdFromDataPackage

End-of-cicle

CompResult

SendReadout cmd

IDLE

Reset

Not(FIFO_Empty &TSMemory_empty)

TS Comparator State Machine

Compare

CompResult = True orNoMoreTStocompare

Exec_cmdFromDataPackage

Stay untilDone or Timeout

Wait command_ack

Slave Header

Package Header ch0

Raw Data

Package Header ch8

Raw Data

.

.

.

Slave Header

Package Header ch0

Raw Data

Package Header ch9

Raw Data

.

.

.

Master Header

Digitizer board output file format