Computer Architecture Question Bank

-

Upload

malikharris -

Category

Documents

-

view

8 -

download

3

Transcript of Computer Architecture Question Bank

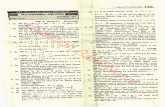

UNIVERSITY EXAM QUESTION PAPERS

B.E./B.Tech. DEGREE EXAMINATION, MAY/JUNE 2009.

Fourth Semester

Computer Science and Engineering

CS 1251 - COMPUTER ARCHITECTURE

(Common to Information Technology)

(Common-to B.E. (Part-Time) - Third Semester- Computer Science and

Engineering - Regulation 2005)

(Regulation 2004)

Time: Three hours Maximum: 100 marks

Answer ALL questions.

PART A - (10 x 2 = 20 marks)

1. What is a system bus?

2. What are the types of memory?

3. Convert the following binary number to decimal number.

(a) 1101012

(b) 1111002

4. What is the purpose of stack?

5. Define pipelining.

6. How are the signed binary numbers represented?

7. Draw the half adder circuit.

8. What is a virtual memory?

9. What are the types of interrupts?

10. Mention the advantage of USB bus.

PARTB - (5 x 16=80 marks)

11. (a) Explain the steps involved in the DMA operation.Or

(b) Describe the various mechanisms for accessing I/O devices.

12. (a) Describe the functional units of the computer system.Or

(b) Explain briefly the various types of addressing modes with example.13. (a) Design the full adder circuit and explain how it is used in the multiplications two signed number.

Or(b) Explain the restoring and non-restoring division algorithm.14. (a) Explain the various pipelining hazards and their remedies in the processor.

Or(b) Describe the multiple bus organization and compare it with single bus organization.

15. (a) Explain the various cache replacement policies in the cache memory.

Or(b) Write a short note on secondary storage devices in computer system.

B.E./B.Tech. DEGREE EXAMINATION, NOVEMBER/DECEMBER2008;

Fourth Semester

(Regulation 2004)

Computer Science and Engineering

CS 1251- COMPUTER ARCHITECTURE'

(Common to Information Technology)

(Common to B.E. (Part-Time) - Third Semester - Regulation 2005)

Time: Three hours Maximum: 100 marks

Answer ALL questions.

PART A - (10 x 2= 20 marks)

1. Draw block diagram of a basic processor.2. Differentiate direct and indirect addressing mode.3. Using 2's complement method perform (10102-11112)4. Write rule for addition in floating point operation.5. Explain structural hazard.6. List the conditions to overcome data hazard.7. Differentiate DRAM and SDRAM.8. Design al MB x 32 bit memory using 256 kB x 8bit static cell.9. 10. Explain handshaking with respect to data transfer.

PART B- (5 x 16 =80 marks)

11. (a) Write the basic performance equation and using this equation explain how the performance of a system can be improved. (16)

Or (b) (i) Explain how the instruction A =B - C gets executed in a system in detail. (8) (ii) Explain briefly stacks and queues. (8)12. (a) Demonstrate the division of 11002 bylOl2 using restoring method, draw block

diagram and explain the operation. (16)Or

b) i) Explain the ripple carry multiplier with (m3m2m1m0)(q3q2q1q0) Inputs. (8) ii) Multiply (-12) and (13) using booths algorithm. (8)13. (a) Explain the operation of hard wired control unit. (16)

Orb) i) Explain how gating is achieved in registers. (6) ii) Discuss in detail about hazards due to unconditional branching (10)

14 a) Explain about direct mapping and set associative mapping in Cache memory.(16)Or

b) Explain about virtual memory and its management.(16)15. (a) i) Explain in detail about direct memory access methods (DMA) (10) (ii) Explain about vectored interrupt with daisy chain arrangement, (6)

Or (b) Write short notes on: (i) Interface circuits

(ii) SCSI(iii) Polling(iv) Addressing of I/O devices. (16)

B.E./B.Tech. DEGREE EXAMINATION, APRIL/MAY 2008.

Fourth Semester

(Regulation 2004)

Computer Science and Engineering

CS 1251 - COMPUTER ARCHITECTURE'

(Common to Information Technology)

(Common to B.E. (Part-Time) - Third Semester - Regulation 2005)

Time: Three hours Maximum: 100 marks

Answer ALL questions.

PART A - (10 x 2= 20 marks)1. What are tri-state gate?2. Why is the data bus in most microprocessors bidirectional while the address bus is unidirectional? 3. Perform 1010100 - 1000100 using 1's and 2's complement.4. Define underflow and overflow.

5. What is pipelining and what are the advantages of pipelining?6. What is the difference between hardwired control and micro programmed control?7. List the differences between static RAM and dynamic RAM.8. Define the terms: spatial locality and temporal locality.9. What factors influences the bus design decisions?10. What is priority interrupt?

PART B- (5 x 16 =80 marks)11. (a) (i) With a neat diagram explain Von-Neumarm computer architecture (12) (ii) What are the major instruction design issues?(4)

Or (b) (i) Explain various instruction formats in detail.(10) (ii) What is a stack and what are the operations on stack? Give any three

applications of stack. (6)

12. (a) (i) Design a 4-bit binary adder/subtractor and explain its function(8) (ii) Give the algorithm for multiplication of signed 2's complement numbers and

illustrate with an example. (8)Or

(b) (i) Design an array multiplier that multiplies two 4-bit numbers and explain its operation. (8)

(ii) Write the algorithm for division of floating point numbers and illustrate with an example. (8)

13. (a) (i) What is branch hazard? Describe the methods for dec1hng with the branch hazards. (10)

(ii) With a suitable diagram describe the sequence of micro operations involved in fetching and executing a typical instruction. (6)

Or (b) What is data hazard? Explain the methods for dealing with the data hazards.(16)14. (a) (i) Describe the functional characteristics that are common to the devices used to

build main and secondary computer memories.(6) (ii) Explain various mechanisms of mapping main memory address into cache

memory addresses. (10)Or

(b) (i) Explain how the virtual address is converted into real address in a paged virtual memory system. (10)

(ii) Describe the working principle of a typical magnetic disk. (6)15. a) Draw the typical block diagram of a DMA controller and explain how it is used

for direct data transfer between memory and peripherals. (16)Or

b) i) Describe the working principles of USB. (8) (ii) Briefly compare the characteristics of SCSI with PCI (8)

B.E./B.Tech. DEGREE EXAMINATION, NOVEMBER/DECEMBER 2008.

Sixth Semester

(Regulation 2004)

Electronics and Communication Engineering

CS 1251- COMPUTER ARCHITECTURE

(Common to B.E. (Part-Time) Fifth Semester Regulation 2005)

Time: Three hours Maximum: 100 marks

Answer ALL questions

PART A - (10 x 2 = 20 marks)

1. Narne the functional units of a computer and how they are interrelated.2. When addressing mode will be viewed critically?3. How do you ascertain an adder as "fast"?4. What is a signed number? Where it is used?5. What is meant by a multiple bus? Where it is organised?6. Define data hazards.7. What is a superscalar operation?8. What is the principle of semiconductor memory?9. What is an non-maskable interrupt? What is the action performed on receipt of a NMI?10. What are the advantages of USB interface?

PART B - (5 x 16 = 80 marks)11. (a) (i) What are the softwares used in a computer to operate all the functional units?

Discuss briefly on the bus structures. (ii) Discuss the operations of a bus. (iii) Calculate the number of memory addresses for a 4 MB memory with a 16 bit

word. (6+6+4)Or

(b) Describe instructions of a computer and how they are sequenced. How is memory organization related to this? (6 + 6+4)

12. (a) Explain an algorithm to multiply two positive numbers. Also discuss the realization of a multiplier to implement the same.(16)

Or (b) How different arithmetic and logic functions are realized and integrated in an

ALU? Explain. (16)13. (a) What is hardwired control? Explain micro-programmed control and compare it

with hardwired control. Which is preferred under what circumstances? (16)Or

(b) Explain the concept of Pipelining. Discuss the influence of various pipelining hazards on instruction set. (16)

14. (a) Describe the working principle of RAM, ROM and cache memories. Compare them based on their speed, size and cost. (16)

Or (b) What is virtual .memory? Explain the various memory management schemes.

What is the need for different memory management schemes? (16)15 a) Describe DMA and its implementation. State the advantages of DMA over the

other modes of I/O transfer. (16)Or

b) Write short notes on(i) Interrupts(ii) Standard I/O interfaces. (16)

B.E./B.Tech. DEGREE EXAMINATION, MAY/JUNE 2007.

Sixth Semester

(Regulation 2004)

Electronics and Communication Engineering

CS 1251 - COMPUTER ARCHITECTURE

(Common to B.E. (Part-Time) Fifth Semester - Regulation 2005)

Time: Three hours Maximum: 100 marks

Answer ALL questions.

PART A- (10 x 2 = 20 marks)

1. The memory unit of a computer. has 256 K words of 32 bits each. The computer has an instruction format with four fields: an operation code field, a mode field to specify one of seven addressing modes, a register address field to specify one of 60 processor registers, and a memory address. Specify the instruction format and the number of bits in each field if the instruction is in one memory word.

2. What is meant by the stored program concept? Discuss.

3. Discuss the principle behind the Booth's multiplier.4. What is a ripple carry adder?5. Discuss the principle of operation of a micro programmed control unit?6. What is the ideal speedup expected in a pipelined architecture with 'n' stages?

Justify your answer.7. Define Average Memory- Access Time for a computer system with two levels of

caches.8. How do you construct a 8 M x 32 memory using 512 K x 8 memory chips?9. What are the functions of a typical I/O interface?10. How does the processor handle an interrupt request?

PART B - (5 x 16 =80 marks)

11 a i) What are the various types of Instruction Set Architectures possible? Discuss. (8) ii) Discuss the various issues to be considered while designing the ISA of a

processor. (8)Or

(b).(i) What is a stack? State some uses of the same. Show how a stack can be implemented using auto increment and auto decrement addressing modes. (8)

(ii) Write an assembly language program using the assembly language you are familiar with to add a sequence of n numbers. Give appropriate comments. (8)

12 a i) Discuss the principle of operation of carry-look ahead adders. (8) (ii) Discuss the non-restoring division algorithm. Simulate the same for 23/5. (8)

Or(b) (i) Discuss the concept of bit pair recoding.

Multiply the following pair of signed 2's complement numbers using bit-pair recoded multiplier Multiplicand 110011 and Multiplier = 101100. (8)

(ii) Simulate the addition and subtraction operations (A + (OR) - B) on the operands:A =.0 10001 011011B =1 01111101010

with a five-bit signed excess-15 exponent and a six-bit normalized fractional mantissa. (8)

13. (a) Give the organization of a typical hard wired control unit and explain the functions performed by the various blocks. Discuss the data flow for a sample instruction. (16)

Or b) Discuss the various hazards that might arise in a pipeline. What are the remedies

commonly adopted to overcome/minimize these hazards? (16)

14 a) i) Discuss the various mapping techniques used in cache memories. (8) (ii) A computer system has a main memory consisting of 16 M words. It also has a

32K-word cache organized in the block-set-associative manner, with 4 blocks per set and 128 words per block.

Calculate the number of bits in each of the TAG, SET and WORD fields of the main memory address format.

How will the main memory address look like for a fully associative mapped cache? (8)

Or (b) (i) Explain the concept of virtual memory with anyone virtual memory

management technique. (8) (ii) Give the basic cell of an associative memory and· explain its operation. Show

how associative memories can be constructed using this basic cell. (8)I5. (a) Explain the functions to be performed by a typical I/O interface with a typical

input or output interface. (16)Or

(b) (i) Discuss the DMA driven data transfer technique.(8) (ii) Discuss the operation of any two input devices. (8)

B.E/B.Tech. DEGREE EXAMINATION, APRIL/MAY 2008.

Sixth Semester

(Regulation 2004)

Electronics and Communication Engineering

CS 1251 - COMPUTER ARCHITECTURE

(Common to B.E. (Part-Time) Fifth Semester Regulation 2005)

Time: Three hours. Maximum: 100 marks

Answer ALL questions.

PART A- (10 x 2 = 20 marks)

1. Registers R1 and R2 of a computer contain the decimal values 1200 and 4.600. What is the effective address of the memory operand In each of the following instructions?

(a) Load 20(R1), R5(b) Add-(R2), R5.

2. What is the use of Condition Code register?3. What do you mean by End-around carry correction?4. Discuss the role of Booth algorithm in the design of Fast Multipliers.5. Why is the Wait-for-Memory-Function-Completed step needed when reading from or

writing to the main memory?6. Write the sequence of control steps required for three bus structure for the following

instruction:Add R4, R5, R6.

7. Define Locality of Reference.8. Give the features of a ROM cell.9. What is the difference between a Subroutine and an Interrupt – service routine?10. Define Bus Arbitration.

PART B - (5 x 16 = 80 marks)

11. (a) Explain in detail the different Instruction types and Instruction Sequencing.(16)Or

b) Explain the different types of Addressing modes with suitable examples. (16)12. a) Illustrate Booth Algorithm with an example. (16)

Or b) Design a 4-bit Carry-Look ahead Adder. (16)

13 a) Write a Microroutine for the instruction Add (Rsrc) + Rdst where the source and destination operands are specified in indexed and register addressing modes, respectively. (16)

Or (b) Explain Microprogrammed Control Unit. What are the advantages and

disadvantages of it? (16)14. (a) Define Cache Mapping Functions. Explain the methods. (16)

Or (b) How does a virtual address gets translated into a physical address. Explain in

detail with a neat diagram. Explain the use of TLB. (16)15. (a) Explain the use of DMA Controllers in a computer system with a neat diagram.

(16)Or

(b) Explain Handshake protocol. Depict clearly how it controls data transfer during an input operation. (16)

B.E./B.Tech. DEGREE EXAMINATION, NOVEMBER/DECEMBER 2007.

Sixth" Semester

(Regulation 2004)

Electronics and Communication Engineering

CS 1251 - COMPUTER ARCHITECTURE

(Common to B.E. (Part-Time) Fifth Semester Regulation 2005)

Time: Three hours Maximum: 100 marks

Answer ALL questions.

PART A - (10 x 2 = 20 marks)

1. Draw the structure of alternative two - bus structure.2. What is mean by straight -line sequencing?3. Draw the structure of 4-bit MSI ALU circuit block.

4. Define IEEE floating point Single and Double precision standard.5. Draw the structure of two stage instruction pipe line.6. What are the limitations on super scalar device?7. Draw the connection between main memory and CPU.8. Write the two advantages of MOS devices.9. What are the necessary operations needed to start an I/O operation using DMA. 10. What are the three types of channels are usually found in large computers?

PART B - (5 x 16 =80 marks)

11. (a) Explain in detail about functional unit and Bus structures of computer (16)Or

(b) Describe various addressing modes with suitable examples. (16)12. (a) With a neat sketch, Explain in detail about logic design for fast address. (16)

Or (b) Describe how the floating - point numbers are represented and used in digital

arithmetic operations. Give an example. (16)13. (a) Explain in detail about instruction execution characteristics. (16)

Or b) With a block diagram, Explain in detail about micro programmed control and

explain its operations. (16)14 a) Give the structure of semiconductor RAM memories. Explain the Read and Write

operations in detail. (16)Or

b) Describe in detail about the memory mapping between virtua1 and main memory with an example. (16)

15. (a) Explain in detail about interrupt handling. (16)Or

(b) Explain in details about standard I/O interfaces. (16)