Chasis Na7d A

-

Upload

baloncesto-usuluteco -

Category

Documents

-

view

117 -

download

17

Transcript of Chasis Na7d A

ORDER NO. MTNC010309G1B1 & B5

Copyright 2001 by Matsushita Electric Corporation of America.All rights reserved. Unauthorized copying and distribution is aviolation of law.

Technical Guide

COLOR TELEVISION SYSTEM

NA7D/A CHASSIS

Please file and use this TECHNICAL GUIDE forthe NA7D/A CHASSIS together with the MainService Manuals and other publications relatedto models based on the NA7D/A chassis.

– 2 –

Notes

– 3 –

Description of Boards ....................................... 4

New TechnologyMPU ..................................................................... 6

Analog Front-end Block................................... 9Y/C Separation ................................................ 9ACC............................................................... 10Luminance Processor.................................... 11Blackstretch Circuits...................................... 11Sharpness Control......................................... 12Chroma Processor Block............................... 12Killer .............................................................. 12Color.............................................................. 12Cb/Cr to R-Y/B-Y Conversion........................ 12RGB Matrix Block .......................................... 13ACL ............................................................... 13Gamma (γ) Correction ................................... 13Mute .............................................................. 13OSD Function................................................ 13Analog Back-end Block ................................. 14Deflection Block............................................. 14Sync Separation ............................................ 14H SYNC SEPA (auto slicer) .......................... 14V SYNC SEPA .............................................. 14AFC1 ............................................................. 14AFC2 ............................................................. 15V Counter ...................................................... 15

Functional Block DiagramsAudio Signal Path............................................. 18Video & Sync Signal Path ................................ 19I2C Bus Line System........................................ 20MPU Control...................................................... 21

AudioMTS Sound Detection and Separation .......... 24

Composite Signal .......................................... 24

Mono or L+R Signal ...................................... 24L–R Signal .................................................... 24Secondary Audio Program (SAP) mode ....... 24dbx® Effect.................................................... 24Matrix Circuit ................................................. 24

AGC Audio Control Surround......................... 26IC2501 Audio Controller................................ 26AGC .............................................................. 26AI Sound ....................................................... 26

Audio Multiplex System................................... 27Abstract......................................................... 27The North American System......................... 27Audio Amplifiers ............................................ 28

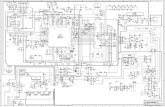

DeflectionDeflection Circuit ............................................ 30

Vertical Output Circuit .................................. 30Sawtooth Wave Generating Circuit .............. 30Drive Circuit ................................................. 30Vertical Output Pulse Amplifying Circuit ...... 31Vertical Output Circuit Operation ................. 31Pulse Amplifier Circuit

(Pump Up) Operation ............................... 31Horizontal Output Circuit............................... 32Horizontal Output .......................................... 32Horizontal Drive Circuit ................................. 33

Power SupplyPower Supply Overview (US Models) ...................................................... 36Power Supply Overview(CT-G3349L)...................................................... 37Protection Circuits ........................................... 38

Over Current Protection ................................ 38Spot Killer...................................................... 38Neck Protector .............................................. 38

The purpose of this Technical Guide is to present an overall view of the circuits used in the NA7D/AChassis. The guide can assist the service technician in troubleshooting a receiver. By using generalblock diagrams, the guide provides the technician with an overall view of the entire system.

The block diagrams include a general description of circuits. The purpose of the descriptions is to helpthe technician understand how particular circuits operate.

By using block diagrams and circuit descriptions, the Technical Guide will help the technician developknowledge about this Chassis.

Table of Contents

– 4 –

Description of Boards Used on the NA7 Chassis

Table 1 lists the various boards and their functionswhich may be used on any of the receivers based onthe NA7 Chassis.

TABLE 1: PANEL DESCRIPTIONS

B-PANEL (TNP2AA079)

SURROUND SOUND CONTROLBASS/TREBLE/BALANCE CONTROL

C-PANEL (TNP2AA075 & TNP2AA086)

RGB DRIVES

J-PANEL (TNP2AA093)

HALF TONE SWITCHING

A-PANEL (TNP2AH031 & TNP2AH024)

AUDIO/VIDEO AND S-VHS INPUT TERMINALSVIDEO SWITCHINGMTS PROCESSINGHALFTONE SWITCHING POWER SUPPLIESMICRO PROCESSOR CONTROLSAUDIO AMPLIFICATIONVERTICAL AND HORIZONTAL DEFLECTION

CONTROLSPROTECTION CIRCUITRY

Z-PANEL (TNP2AA010)

PINCUSHION CORRECTION

P-PANEL (TNP2AA014)

DC - DC CONVERTOR POWER SUPPLY

COLOR TELEVISION SYSTEM

NA7D/A CHASSIS

NEW TECHNOLOGY

– 6 –

M65580MAP100 (MPU/VCJ)

The MPU/VCJ employed in the NA7D/A chassisincorporates processes that on other chassis areperformed by other ICs. These functions includesynchronization, TV, EXT, Y/C switching, VideoChroma Jungle (VCJ) and filtering. Fig. 2 & Fig. 3

display the block diagram for the IC as a whole andin detail respectively.

Figure 1: MPU/VCJ Pinout

– 7 –

Figure 2: MPU/VCJ Block Diagram

– 8 –

Figure 3: MPU/VCJ Block Diagram (for Signal Processing)

– 9 –

Analog Front End Block (Fig. 4)

The MPU, via the I2C Bus data, selects theappropriate input from the TV_In, EXT_In or Y/C_In.CVBS or Y signal is amplified to twice the inputsignal and output from pin 18 to pin 17 for SyncSeparation block and to pin 77 for CC DEC. WhenStandard Analog Composite (CVBS) signal isselected for input, it is input to the first 8bit ADC.When Y/C signal is selected for input, the Y portionis input to the first 8bit ADC and the Chroma is input

to the second 8bit ADC. The signals are thenconverted to digital signals.

The reference voltage can be either 1.7V (1.2Vp-p),1.8V (1.3Vp-p) or 1.9V (1.4Vp-p), selected by the

MPU, via the I2C BUS data. The timing of the ADCand Logic CLK can be changed by the MPU, via the

I2C Bus data.

Figure 4: Analog Front End Block

Y/C Separation (Fig. 5)

A two-dimensional YC separation is performed using1 line memory and an algorithm. Input CVBS signalis fed in to a filter (H-BPF) in the horizontal directionand the filter (HV-BPF) in the horizontal-verticaldirection for detecting in which direction (H or V) theinput signal correlates. When there is no correlationin the vertical direction the filter is changed from HV-BPF to H-BPF. The sensitivity of the correlationdetection can be adjusted by the MPU, via the I2CBUS. Regardless of correlation detection H-BPF or

HV-BPF can be selected by the MPU, via the I2CBUS. This circuit is effective only when input CVBSis larger than a determined level. If the level is small,the Luminance signal is filtered by Trap around FSCfrequency and the Chrominance is filtered by Y/Cseparator. In case of Y/C input, the circuit will bypassthe process by the MPU, via the I2C BUS. Y&Csignals are passed to the Y processing block and theC processing block respectively.

Figure 5: Y/C Separation

– 10 –

ACC (Fig. 6a & Fig. 6b)

This IC contains digital ACC to boost input. If burst

level is smaller than the level of MPU, via the I2CBUS, three analog ACC amps, each of 10dB operatein order. The on/off status is also controlled by the

MPU, via the I2C BUS, as follows:0 = amp off: 0dB1 = ampx1 on: 10.5dB

2 = ampx2 on: 21dB3 = ampx3 on: 31.5dBWhen the third analog ACC amp is on, digital ACC

circuit can be set to off by the MPU, via the I2C BUS.It can also be forced to be in the off state by the

MPU, via the I2C BUS.

Figure 6a: ACC Processing

Figure 6b: ACC Processing

– 11 –

Luminance Processor (Fig. 7)

In this process, the Y/C delay timing, blackstretch,YNR, sharpness of input luminance signal is

controlled by the MPU, via the I2C data, the followingway:

Y/C delay adjustment: luminance signal can bedelayed to adjust to chroma signal delay time by

MPU, via the I2C BUS data. The YNR functionsubtract noise at around fsc frequency fromluminance signal.

Figure 7: Y/C Separation

Blackstretch CircuitsThe IC has detection for input Y signal in dot, fieldand time dimension. Fig. 8 details the process.

Figure 8: Blackstretch CircuitsOne of the status can be selected for white area of Yinput signal. Each status is determined by the uppersystem, and it can also be checked by the MPU, via

the I2C Bus, or IM (Intelligent Monitor) terminals(pin 11). Fig. 9 displays the process of the blackstretch.

YC Separation

Normal 2 Line Comb Filter

Weak Signal Y: Trap Filter (Digital)

C: Band Pass Filter (BPF, Digital)

Input Block Amp is ON

Small Burst Signal (Chroma)

– 12 –

Figure 9: Blackstretch Process

Sharpness ControlPreshoot and overshoot signals are added to theinput luminance signal to emphasis on the outline ofthe picture. The width and gain of the preshoot and

overshoot can be controlled by the MPU, via the I2CBUS, as well as the upper limit of the sharpnesslevel.

Chroma Processor Block (Fig. 10)

Input chroma is converted to R-Y & B-Y signals byoffset canceller, demodulator ACC, Color, Tint andKiller circuits.

When color signal is present, input chroma isdemodulated by 4fsc CLK to input burst signal andcalculation of its components. Tint is controlled by

the MPU, via the I2C BUS data.

Figure 10: Chroma processing

KillerWhen the burst level is smaller than Killer level set

by the MPU, via the I2C BUS, in succession of twofields, it is switched to Killer-on (Chroma outputOFF). It can also be forced to switch by the MPU, via

the I2C BUS. The switching between on and off isdone on a condition of hysteresis and interval. Killerdetection is also done by noise detection and Vcoincidence.

Color

Color level is controlled by the MPU via the I2C BUS.

Cb/Cr to R-Y/B-Y ConversionFollowing is the conversion formula in which thenormalized Cb/Cr signals are converted to R-Y/B-Y:

R-Y=1.14 x Cr

B-Y=2.03 x Cb

– 13 –

RGB Matrix Block (Fig. 11)

The Y, R-Y & B-Y signals that are input to the IC areprocessed by the RGB matrix to generate the R, G &B signals by the following formula:

R = 1 x Y + 0 x (B-Y) + r x (R-Y)

G = 1 x Y - (13/16) x (B-Y) - (7/16) x (R-Y)

B = 1 x Y + 1 x (B-Y) + 0 x (R-Y)

where r = 12/8, 13/8, 14/8

If the result is negative, the output is clipped to“000h”. Level can be fixed to 0 (LSB) by Mute of

MPU, via the I2C BUS.

Figure 11: RGB Matrix

ACLThe R/G/B signals are multiplied with ACL data andContrast data (6 & 7 bit respectively). The signalsare clipped when they exceed a maximum level,then data is divided by a constant. Contrast and ACL

data are set to fixed levels in standard case. Databelow a certain level is fixed to a predeterminedlevel for only OSD signal when F.B. signal = 1.

Gamma (γ) CorrectionGamma points (16 kinds) and on/off/inverse/no-inverse mode of R/G/B signals are controlled by the

MPU, via the I2C BUS. See Fig. 12.

Figure 12: Gamma (γ) Correction

Mute

On/off of R/G/B is controlled by the MPU, via the I2CBUS data.

OSD FunctionInput picture data R/G/B are overlaid by RGB OSD(through Q050 ~ Q052) F.B. and half tone signalsfrom the MCU block through IC050.

OSD overlay and halftone (transparent) are twokinds of display modes in OSD function.

Note: Gamma on/off can be controlled byMPU via the I2C.Gamma Point (circle) can be adjustedby 64LSB steps from 64LSB to960LSB by MPU via the I2CIt has inverse mode (Line-B) and noninverse mode (Line-A).

– 14 –

Analog Back-end Block9 bit Cut-off DACs and 7 bit Drive DACs control the 3channels 10 bit high speed video DACs for main

R/G/B signals. R/G/B output are also controlled forSpot killer. See Fig. 13.

Figure 13: Analog Back-end Block

Deflection BlockThe signal for synchronization of the input video isgenerated in this area as well as the horizontal andvertical synchronization. It contains two phaselocked loops, AFC1 & AFC2. AFC1 generates thehorizontal and vertical timing pulse. Phase andfrequency are synchronized by the input sync. The H

SYNC generated at AFC1 is the reference timing forall data related to display. AFC2 is used to adjust thephase of the horizontal drive pulse andcompensation for the delay of the horizontal outputstage such as FBT.

Sync Separation:The Sync Separation is composed of H SYNC SEPAwhich extracts COMPOSITE SYNC from input

CVBS signal and V SYNC SEPA which extracts VSYNC from COMPOSITE SYNC.

H SYNC SEPA (auto slicer)The input CVBS signal is clamped to pedestal levelby BGP (burst gate pulse) generated at DEF LOGICblock. The center voltage of the pedestal voltage

and the sync tip voltage is generated. COMPOSITESYNC can be separated by comparing the centervoltage with the input CVBS.

V SYNC SEPADuring the period “H” of COMPOSITE SYNC(negative polarity), the capacitor is charged, and inthe period “L”, it is discharged with the determinedcurrent in the IC. The wave like triangle is generated

in the horizontal period. V SYNC can be separatedby comparing the triangle waveform with thedetermined voltage. Only the pulse over thedetermined time is identified as V PULSE.

AFC1AFC1 is composed of freerun frequency adjustmentand fH pulse. Free running frequency of HVCO isadjusted to around 15.73KHz by VCO control circuitof which standard frequency is 4fsc (=14.32MHz).The free running frequency can be changed by

MPU, via the I2C BUS. fH pulse generated by

division of the HVCO, is compared in phase with theinput H SYNC to synchronize. BGP for SYNC SEPA,HD pulse for signal processing, timing pulses forAFC2 are generated in this stage. The gain of AFC1

can be changed by the MPU, via the I2C BUS data,and the state of COINCIDENCE. See Fig. 14.

Figure 14: AUTO ADJ & AFC1

– 15 –

AFC2Two timing pulses for H-RAMP (corresponding to therising and falling edges of HOUT) generated inAFC1 stage are applied to the delay circuitcontrolled by the voltage. H-pulse (HOUT) isgenerated by this circuit. HOUT is fed back to thisstage as a reference pulse (FBP) through the

horizontal drive circuits (H drive Tr, FBT, etc.). Thephase of HOUT can be adjusted by comparing FBPwith the output of divider in AFC1 and control thethreshold voltage of delay circuit. The phase of FBPis adjusted to be in the blanking period of the inputCVBS signal.

Coincidence

In the period of SYNC SEPA and for FBP is “H”, acapacitor is charged by the current. During “L” thecapacitor is discharged. The voltage at the capacitoris check. During “LOCK”, the output of the detectoris “H”. During “UNLOCK” the output of the detector is“L”. The detector has a fast and slow modes. The

slow mode is output by the MPU, via the I2C BUS,

and the killer circuit is set to on. Fast mode is usedfor skew distortion of VTR at the upper side of theTV screen. Loop gain is controlled by AFC1 by theskew and unlock detection. If AFC is in “LOCK” andphase is not within acceptable range then the skewat the upper side of the screen is compensated byselecting a higher AFC1 gain.

V COUNTER

In the vertical period, the counter by 2fH CLK rate isused. The circuit extracts only pure vertical timingpulse from V SYNC SEPA signal is generated in VSYNC SEPA stage. When abnormal vertical pulsesare encountered they are ignored.

The counter is reset by the input vertical signal andoutput the reference pulse to Vramp circuit. In thatprocess the counter is operated by 2fH clock andwhen the number of counter is over a predetermined

limit, the next V pulse is not ignored. When V SYNCSEPA output is missing, V pulse is regenerated bythe determined timing (window function). V counteris reset by itself when no V SYNC SEPA signal isreceived and stop receiving the signal for adetermined period. This circuit also has a function of“V shift” to adjust vertical position of screen and “VCOINCIDENCE” to detect if V counter is locked orunlocked.

X-ray and Neck Protector

The X-ray protector can be set to non-active state by

the MPU, via the I2C BUS. When the voltage atpin 36 is higher than the first threshold voltage(VthHD), the frequency of Hout is fixed to about16.5KHz. When it is higher than the secondthreshold voltage (VthSD), Hout is stopped (nosignal). The threshold voltages can be selected by

the MPU, via the I2C BUS.

If the horizontal high voltage circuit is malfunctioningand the X-ray protector does not work properly, theelectron beam may overheat and melt the CRTneck. Therefore this circuit detects these abnormalstates and shuts down the RGB output. When pin 40is low (0V) the output of the R/G/B is set to zero (nosignal).

Intelligent Monitor

One analog or digital signal can be monitored (Vdd,input of ADCs, Hsync output, etc.) through pin 11.

The signal is selected by the MPU, via the I2C BUS.

– 16 –

Notes

COLOR TELEVISION SYSTEM

NA7D/A CHASSIS

FUNCTIONALBLOCK DIAGRAMS

– 18 –

This section describes the flow diagrams for mainfunctions. Fig. 15 provides the audio signal flow.Fig. 16 provides the video/sync signal flows. Fig. 17details the I2C operation and Fig. 15 ~ Fig. 18include various MPU functions and control.

Other sections provide details and other aspects ofthe operation, such as audio, deflection, powersupplies and protection.

.

Fig

ure

15:

Aud

io S

igna

l Pat

h

– 19 –

Figure 16: Video & Sync signal path

**

See Fig. 30 for

– 20 –

I2C Bus Line SystemThe NA7D/A incorporates an Inter-Integrated Circuit(I2C) double polarity bus (see Fig. 17). The I2C buscarries information between devices connected tothe bus using two lines, the Serial Data (SDA) andSerial Clock (SCL). Each device has an uniqueaddress for data transfer called the Slave Address.

When data is transmitted or received, the devices onthe bus are either a “Master” or a “Slave”. For NA7D/A chassis, the “Master” device is the IC001Microprocessor Unit (MPU). The MPU initiates adata transfer on the bus line and generates the clock

signal that permits data to be sent. The MPU thenaddresses the “Slave” devices, which receive thetransmitted data and return an acknowledgment tothe MPU.

The I2C bus system performs control functions thatreplaces many of the mechanical controls needed ina television receiver. Instead of adjusting individualmechanical controls, electronic control functions canbe performed using the “On Screen Display Menu” inServiceman Mode.

Figure 17: I2C Bus

MCU

MCU

SIGNALPROCESSOR

SIGNALPROCESSOR

SCL

SDA

– 21 –

Figure 18: MPU/VCJ Control

See Fig. 30 for details

– 22 –

Notes

COLOR TELEVISION SYSTEM

NA7D/A CHASSIS

AUDIO

– 24 –

MTS Sound Detection And Separation

Composite Signal

The composite audio signal from the tuner inputs toMTS Decoder IC2201 pin 14 (MPX in) (see Fig. 19).

The signal is processed by a low pass Stereo Filterwhich passes signals below 15.75kHz. The outputfrom the Stereo Filter contains the L+R signal(mono) and may also contain the L-R signal (stereo)plus the Stereo Pilot signal (stereo broadcastindicator). The signal is then applied to four circuits:

• Pilot detector• Stereo PLL• L+R Demod (FM)• L-R Demod (AM)

Mono or L+R Signal

The L+R signal is FM demodulated and then sent tothe L+R Filter. The high frequency components ofthe signal are de-emphasized and sent to the Matrixcircuit for left and right channel simulation.

L–R Signal

When the 15.75kHz stereo pilot signal is detected atpin 6, indicating AM stereo broadcast, the stereoPLL switches on the L-R Demod to demodulate theAM signal.

The signal is then passed to the L-R Filter whichremoves the high frequency noise components.

The signal is then passed to the L-R/SAP switch,which is controlled by I2C bus user input (Stereo orSAP), and output to pin 15.

The signal from pin 15 is coupled via an externalcapacitor to pin 16 and applied to the dbx circuit.

Secondary Audio Program (SAP) mode

The input signal applied at MTS IC2201 pin 14 (MPXin) is fed to the SAP Filter and the Noise band passfilter (BPF). The Noise BPF removes componentsaround 240 kHz.

If Stereo is selected, the signal is passed through theSAP Noise Detector to the SAP Demod to mute theSAP demodulator.

If SAP is selected, the SAP signal is demodulated,filtered for noise components, output via pin 13, andapplied to the dbx circuit via pin 12.

dbx ® Effect

dbx is a compression, expansion, pre-emphasis, de-emphasis system that reduces the overall audionoise level. As the overall level in the audio chainincreases, the noise level increases also. With dbx,the audio level increases, but by only half as much.

Using a 2 to 1 compression ratio, the input signal iscompressed and a “shelving” filter is referenced tothe input level to set the pre-emphasis. A shelvingfilter is a circuit with a flat frequency response thathas two bands of frequencies that are separated bya third band. This third band has either a downwardor upward sloping frequency response.

The output signal is decompressed and the highfrequencies are rolled off by the de-emphasis filter.The output audio signal now has a greater S/N thenthe input signal. It has a flat frequency response andup to 30 dB less noise.

Note: MTS IC2201 pin 10 is the timing currentsetting of the dbx rms value detection, andis set at about 1.3V. Pin 6 is the referencepower supply stabilization voltage, and isset at about 4.5V.

dbx is a registered trademark of Carillon ElectronicsCorp.

Matrix Circuit

The matrix circuit switches the output audio signalaccording to the selection received from MPU IC001through the I2C bus at pins 19 (SDA) and 18 (SCL).The signals are output through pins 21 (L-out) and22 (R-out) to the sound switching circuit.

Selection Matrix Effect

Mono L+R or mono to output to pins 21 & 22

Stereoto pin 22

to pin 21

SAP SAP to output to pins 21 & 22

L R+( ) L R–( )+2

--------------------------------------------

L R+( ) L R–( )–2

-------------------------------------------

– 25 –

Figure 19: Multiplex Television Sound (MTS)

– 26 –

Figure 20: AGC Audio Path

AGC Audio Control Surround

IC2501 Audio Controller

IC2501 Audio Controller/Sound Processor controlsall aspects of the sound via the MPU: bass, treble,balance, AGC, AI Sound, and Mute (see Fig. 20).

AGC

At times the received audio signal level is too high ortoo low, so special circuits are needed to equalizeaudio levels across various programming.

AGC is designed to detect and compensate for thelarge variations in audio input levels across TVchannels and other sound sources connected to theAV jacks. When AGC is on, the input/output gain isboosted for low signal levels and reduced for highsignal levels (see Fig. 21).

Figure 21: AGC Effect on Sound

The circuit detects level changes via AGC Det 1,which outputs to AGC Det 2 (Control circuit) toprovide a gain factor for both left and right channel

AGC circuits. At a level predetermined by the RCnetwork on IC2501 pin 5, the internal switch togglesthe contacts and adjusts the gain to the outputterminals.

Bass, Treble, Balance

When a user makes an adjustment to the audiooutput via the front keyboard or the remote control,data from the MPU is clocked (at 12 MHz) via theI2C bus to the IC2501 I2C interface at pins 16 and17. Pulse width modulation switching controls whichDAC will be applied to the audio signal.

AI Sound

The IC2501 AI Sound circuit uses an algorithmbased on the difference in frequency characteristicsbetween music and speech (see Fig. 22 andFig. 23). The circuit is incorporated by simplehardware and microprocessor control to equalize thesound level across inputs and automatically controlsbass and treble to the optimum degree.

Continuous speech consists of repetitions of aconsonant, a vowel and silence. Power levelschange rapidly. Consonants have large changes inpower level and spectrum; vowels are steadier, withsmaller changes.

Musical sounds have relatively small changes inpower and spectrum, with longer steady parts.

– 27 –

Figure 22: AI Audio Algorithm

The original waveform (speech or music) is sent to alevel rectifying circuit, a waveshaping circuit, andthen is fed to the microprocessor. The

microprocessor samples the waveform and setsthreshold values, then makes judgements whetherto boost bass and treble for music or reduce them forspeech.

Figure 23: AI Audio Frequency Response

Audio Multiplex System

Abstract

In audio multiplex broadcasting, a separate soundsignal, unrelated to the broadcast content, is sent inaddition to the monaural sound. This is done in orderto accomplish transmission of stereo signals and isachieved via frequency multiplex technology. Intoday’s broadcast, the traditional L + R and L - Rsignals are sent. The signals are monitored,cleaned, decompressed and finally separated in thematrix circuit to the L and R components.

Matrix: (L+R) + (L-R) = 2L(L+R) - (L-R) = 2R

The North American System

The North American Television sound system iscomposed of three types of modulation: FM, FMMultiplex (stereo and SAP) and AM (see Fig. 24).

Monaural Broadcasting: Monaural sound (L + R) issent as ±25kHz FM signal in the 4.5MHz audiocarrier wave.

Multiplex Broadcasting: The L (left) and R (right)signals are sent in two different “packets” in additionto other required signals. The multiplex signal hasfour components:

• L + R - identical to the monaural signal.

• L - R - amplitude modulated with a centerfrequency of 35.1kHz (twice the horizontalfrequency of 15.75kHz.)

• Secondary Audio Programming (SAP) - FMmodulated (+/- 15kHz) with a centerfrequency of 78.75kHz (5fh).

• Stereo pilot - FM signal at 15.75kHz (±5kHz).

– 28 –

Figure 24: North American MultiplexAudio Amplifiers

Fig. 25 depicts the process in which the audioamplifiers operate. The MPU controls the volumeand mute operation. The amplified signals output at

pin 10 and is sent to the speakers. Note that on amono receivers only the left audio amplifier isoperational, sending the signal to the single speaker.

Figure 25: Audio Amplifiers

fH 2fH 3fH 4fH 5fH

AM

FM

f (Hz)

2 (L - R)

L + R

SAP

±25kHz

±50kHz

±15kHz

fH = 15.75kHz

FMS

T P

ilot S

igna

l5k

Hz

±Car

rier

Dev

iati

on

COLOR TELEVISION SYSTEM

NA7D/A CHASSIS

DEFLECTION

– 30 –

Deflection Circuit

Vertical Output CircuitSawtooth Wave Generating Circuit

The vertical sync pulse at pin 2 creates a timingsawtooth wave in C452 (see Fig. 26). Thisdetermines the amplitude of the voltage at pin 4,which is controlled by pin 68 of the MPU. Thisadjustment is available in service mode. The voltageat pin 4 sets the 50-60 Hz amplitude for the voltageat pin 5. The vertical drive corrects the rectilinearstraightness, vertical amplitude and pulse amplitudein the same IC.

Drive Circuit

1. The sawtooth wave is sent to the vertical drivecircuit. The wave current in the verticaldeflection coil is fed back to pin 7 to improvethe vertical straightness of the signal.

2. The vertical drive section of IC451 amplifiesthe sawtooth wave to correct for straightnessof the wave so the vertical output circuit willoperate. The corrected wave is sent to thevertical output circuit.

Figure 26: IC451 - Vertical Deflection Circuit

– 31 –

Vertical Output Pulse Amplifying CircuitVertical Output Circuit Operation

1. The sawtooth wave voltage from the verticaldrive circuit is inverted in Q1 and input to Q2and Q3 (see Fig. 27).

2. The Q2 and Q3 threshold voltage is set to thecenter of the sawtooth wave. The first half ofthe wave turns on Q2, resulting in the chargingcurrent (a) being sent to C1 (see Fig. 28).

3. The second half of the wave turns on Q3,resulting in the discharge current (b) beingoutput from C1.

4. A sawtooth wave current is sent to thedeflection coil. However, to reverse the currentwithin the vertical flyback period, the pulsefrom the pulse amplifier circuit is added to thecollector of Q2. This results in a large voltage

input to the deflection coil during the instantafter Q2 is turned on.

Pulse Amplifier Circuit (Pump Up) Operation

1. When currents (a) and (b) are sent (during thevertical scanning period), Q4 is off because novoltage is input to its base. A negative pulsefrom the vertical deflection coil is fed back tothe base of Q5, which turns Q5 on. 26V aresent through D1, which inputs a 26V charge toC2.

2. The differentiated pulse during the flybackperiod is added to the base of Q4 and Q5,turning Q4 on and Q5 off. 26V is input to C2negative (-) pin through Q4 and added to the26V C2 charge, resulting in a 52V pulse atpin 13 (see Fig. 29).

3. The 52V pulse is input to the deflection coil,raising the electron beam in one instant.

Figure 27: IC451 - Vertical Output Pulse Amplifying Circuit

Figure 28: IC451 pin 12 Voltage Figure 29: Pump Up Wave

Voltage input to the Deflection Coil Q1 Collector Differential

Q2 ON Q3 ON Waveform ofQ4-Q5 base Pin 9 voltage

Pin13 voltage

– 32 –

Horizontal Output Circuit

Horizontal Output

The square wave of the horizontal signal sent by theMPU is applied to Q501, the horizontal drive.

That turns Q501 on (see Fig. 30). 130 volts flowsthrough the primary of T501 and the horizontal drive,Q501. A horizontal pulse is induced into the

secondary windings of T501. This pulse drives thehorizontal output Q551 to make the sawtooth wavecurrent in H-DY (horizontal deflection coil) and EHT(extra high tension voltage).

Figure 30: Horizontal Drive and Output Circuit

– 33 –

Horizontal Drive Circuit

Figure 31: Horizontal Drive Circuit

– 34 –

Notes

COLOR TELEVISION SYSTEM

NA7D/A CHASSIS

POWER SUPPLY

– 36 –

Figure 32: Power Supply Overview (NA7D)

– 37 –

Figure 33: Power Supply Overview (NA7A)

– 38 –

Protection Circuits

Over Current ProtectionThe over current protection circuit is designed to preventdamage to the Receiver due to shorts in the 130V line.

During normal operation, current flowing through R821 &R822 produces low voltage across the resistors that isnot sufficient to turn Q820 ON.

When a short occurs, the current through R821 & R822increases, causing a rise in the voltage across theresistors. When the voltage drop reaches the pointwhere Vbe is high enough to turn Q820 ON, a signal issent by Q820 to the MPU pin 9 (KEY2). The MPU thenshuts the Receiver OFF.

Spot KillerThe spot killer circuit is designed to prevent the highintensity beam that could form at the center of the screenin an event of abnormal power loss.

The circuit is made up of Q605, Q606 and relatedcomponents.

During normal operation, the high voltage at the base ofthe PNP transistor, Q605, keeping it OFF. When Q605 isoff, it keeps Q606 OFF. Under these conditions, C606 ischarged when Q606 is OFF. That prevents D607 ~ D609

from conducting. That also allows the only path for theRGB current to flow (from Q006 ~ Q008) to the C board,the CRT driver.

When the 12V line goes low due to an abrupt loss ofpower, Q605 & Q606 turn ON and C606 dischargesallowing the output from Q006 ~ Q008 to flow throughD607 ~ D609. Therefore the RGB output signal isprevented from flowing to the C board. See Fig. 34.

Figure 34: Spotkiller Protector CircuitNeck Protector (Fig. 35)

The neck protector protects the CRT in an event ofshorting in the V-out or DY circuits. The circuit consistsof Q451 & Q452 and related components.

During normal operation, the vertical out from IC451conducts through the Zener diode, D452. That keepsQ451 ON and Q452 OFF. A high signal is sent to theMPU pin 40 indicating normal conditions.

When the Vert out of IC451 is low (damage to the IC), itturns Q451 OFF. The base of Q452 is at ~9V, turning itON. Q452 starts conducting, lowering the voltage atMPU pin 40. The MPU senses the change that occurredand it shuts down the RGB output, resulting in a blackscreen

– 39 –

Figure 35: Neck Protector Circuit

Figure 36: Standby Voltage

Figure 37: DC Operation (AC/DC Models Only)

130V

DC Voltage Supply

Power

– 40 –

Figure 38: Degaussing Coil (AC/DC Models Only)

Printed in USAK01032593ZR0330