Bridging Router Performance and Queuing Theory

description

Transcript of Bridging Router Performance and Queuing Theory

www.intel.com/research

Bridging Router Performance and Queuing Theory

N. Hohn*, D. Veitch*, K. Papagiannaki, C. Diot N. Hohn*, D. Veitch*, K. Papagiannaki, C. Diot

*: University of Melbourne*: University of Melbourne

2

www.intel.com/research

• Intel Research •

MotivationMotivation

End-to-end packet delay is an important metric for End-to-end packet delay is an important metric for performance and SLAsperformance and SLAs

Building block of end-to-end delay is through router Building block of end-to-end delay is through router delaydelay

We measure the delays incurred by We measure the delays incurred by allall packets packets crossing a single routercrossing a single router

3

www.intel.com/research

• Intel Research •

OverviewOverview

Full Router MonitoringFull Router Monitoring

Delay Analysis and ModelingDelay Analysis and Modeling

Delay Performance: Understanding and ReportingDelay Performance: Understanding and Reporting

4

www.intel.com/research

• Intel Research •

Measurement EnvironmentMeasurement Environment

5

www.intel.com/research

• Intel Research •

Packet matchingPacket matching

SetSet LinkLink Matched pktsMatched pkts % traffic C2-out% traffic C2-out

C4C4 InIn 215987215987 0.03%0.03%

C1C1 InIn 7037670376 0.01%0.01%

BB1BB1 InIn 345796622 47.00%47.00%

BB2BB2 InIn 389153772 52.89%52.89%

C2C2 outout 735236757 99.9399.93%%

6

www.intel.com/research

• Intel Research •

OverviewOverview

Full Router MonitoringFull Router Monitoring

Delay Analysis and ModelingDelay Analysis and Modeling

Delay Performance: Understanding and ReportingDelay Performance: Understanding and Reporting

7

www.intel.com/research

• Intel Research •

Store & Forward DatapathStore & Forward Datapath

Store: storage in input linecard’s Store: storage in input linecard’s memorymemory

Forwarding decisionForwarding decision

Storage in dedicated Virtual Output Storage in dedicated Virtual Output Queue (VOQ)Queue (VOQ)

Decomposition into fixed-size cellsDecomposition into fixed-size cells

Transmission through switch fabric cell Transmission through switch fabric cell by cellby cell

Packet reconstructionPacket reconstruction

Forward: Output link schedulerForward: Output link scheduler

Not part of the system

8

www.intel.com/research

• Intel Research •

Delays: 1 minute summaryDelays: 1 minute summary

9

www.intel.com/research

• Intel Research •

Store & Forward DatapathStore & Forward Datapath

Store: storage in input linecard’s Store: storage in input linecard’s memorymemory

Forwarding decisionForwarding decision

Storage in dedicated Virtual Output Storage in dedicated Virtual Output Queue (VOQ)Queue (VOQ)

Decomposition into fixed-size cellsDecomposition into fixed-size cells

Transmission through switch fabric cell Transmission through switch fabric cell by cellby cell

Packet reconstructionPacket reconstruction

Forward: Output link schedulerForward: Output link scheduler

Not part of the system

Δ

10

www.intel.com/research

• Intel Research •

Minimum Transit TimeMinimum Transit Time

Packet size dependent minimum delay Δ(L), specific to router architecture and linecard technology

11

www.intel.com/research

• Intel Research •

Store & Forward DatapathStore & Forward Datapath

Store: storage in input linecard’s Store: storage in input linecard’s memorymemory

Forwarding decisionForwarding decision

Storage in dedicated Virtual Output Storage in dedicated Virtual Output Queue (VOQ)Queue (VOQ)

Decomposition into fixed-size cellsDecomposition into fixed-size cells

Transmission through switch fabric cell Transmission through switch fabric cell by cellby cell

Packet reconstructionPacket reconstruction

Forward: Output link schedulerForward: Output link scheduler

Not part of the system

Δ(L)

FIFO queue

12

www.intel.com/research

• Intel Research •

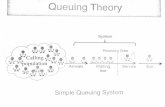

ModelingModeling

13

www.intel.com/research

• Intel Research •

ModelingModeling

Fluid queue with a delay element at the front

14

www.intel.com/research

• Intel Research •

Model ValidationModel Validation

15

www.intel.com/research

• Intel Research •

Error as a function of timeError as a function of time

16

www.intel.com/research

• Intel Research •

Modeling resultsModeling results

Our crude model performs wellOur crude model performs well

Use effective link bandwidth (account for Use effective link bandwidth (account for encapsulation)encapsulation)

Small gap between router performance and Small gap between router performance and queueing theory!queueing theory!

The model defines Busy Periods: The model defines Busy Periods: time between the arrival of a packet to the empty system and the time when the system becomes empty again.

17

www.intel.com/research

• Intel Research •

OverviewOverview

Full Router MonitoringFull Router Monitoring

Delay Analysis and ModelingDelay Analysis and Modeling

Delay Performance: Understanding and ReportingDelay Performance: Understanding and Reporting

18

www.intel.com/research

• Intel Research •

On the Delay PerformanceOn the Delay Performance

Model allows for router performance evaluation Model allows for router performance evaluation when arrival patterns are knownwhen arrival patterns are known

Goal: metrics thatGoal: metrics that

Capture operational-router performanceCapture operational-router performance

Can answer performance questions directlyCan answer performance questions directly

Busy Period structures contain Busy Period structures contain allall delaydelay information information

19

www.intel.com/research

• Intel Research •

Busy periods metricsBusy periods metrics

ts

D

A

20

www.intel.com/research

• Intel Research •

Property of significant BPsProperty of significant BPs

21

www.intel.com/research

• Intel Research •

Triangular ModelTriangular Model

LAifA

LDd T

DAL ),1()(,,

22

www.intel.com/research

• Intel Research •

IssuesIssues

Report (A,D) measurementsReport (A,D) measurements

There are millions of busy periods even on a lightly There are millions of busy periods even on a lightly utilized routerutilized router

Interesting episodes are rare and last for a very Interesting episodes are rare and last for a very small amount of timesmall amount of time

23

www.intel.com/research

• Intel Research •

Report BP joint distributionReport BP joint distribution

24

www.intel.com/research

• Intel Research •

Duration of Congestion Level-LDuration of Congestion Level-L

25

www.intel.com/research

• Intel Research •

ConclusionConclusion

ResultsResults

Full router empirical studyFull router empirical study

Delay modelingDelay modeling

Reporting performance metricsReporting performance metrics

Future workFuture work

Fine tune reporting schemeFine tune reporting scheme

Empirical evidence of large deviations theoryEmpirical evidence of large deviations theory

www.intel.com/research

Thank you!