BR 8/991 DFFs are most common Most programmable logic families only have DFFs DFF is fastest,...

-

Upload

arthur-stevenson -

Category

Documents

-

view

212 -

download

0

Transcript of BR 8/991 DFFs are most common Most programmable logic families only have DFFs DFF is fastest,...

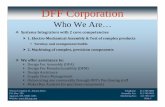

BR 8/99 1

DFFs are most common

• Most programmable logic families only have DFFs• DFF is fastest, simplest (fewest transistors) of FFs• Other FF types (T, JK) can be built from DFFs• We will use DFFs almost exclusively in this class

– Will always used edge-triggered state elements (FFs), not level sensitive elements (latches).

BR 8/99 2

Synchronous vs Asynchronous Inputs

Synchronous input: Output will change after active clock edgeAsychronous input: Output changes independent of clock

DQ

C

S

R

Flip-Flops often have async set, reset control.

D input is synchronous with respect to Clk

S, R are asynchronous. Q output affected by S, R independent of C. Async inputs are dominant over Clk. S,R inputs often called Pre (preset) and Clr (clear) inputs.

BR 8/99 3

DFF with async control

C

D input

Q (FF)

R

S

BR 8/99 4

Flip-Flop, Latch Timing

• Propagation Delay– C2Q: Q will change some propagation delay after

change in C. Value of Q is based on D input for DFF.

– S2Q, R2Q: Q will change some propagation delay after change on S input, R input

– Note that there is NO propagation delay D2Q for DFF!

– D is a Synchronous INPUT, no prop delay value for synchronous inputs

BR 8/99 5

Clock to Q Propagation Delay

C

D input

Q (FF)

Tc2qlh Tc2qhl

There is NO delay from D to Q!!! The clock input is what triggers the change, not the D input!!!

BR 8/99 6

S, R to Q Propagation Delay

C

D input

Q (FF)

S

R

Ts2qlhTr2qhl

BR 8/99 7

Setup, Hold Times

• Synchronous inputs (e.g. D) have Setup, Hold time specification with respect to the CLOCK input

• Setup Time: the amount of time the synchronous input (D) must be stable before the active edge of clock

• Hold Time: the amount of time the synchronous input (D) must be stable after the active edge of clock.

BR 8/99 8

Setup, Hold Time (rising edge triggered)

tsu thd

C

D changing

Stable

If changes on D input violate either setup or hold time, then correct FF operation is not guaranteed.

Setup/Hold measured around active clock edge.

D changing

BR 8/99 9

More on Setup, Hold Times

C

D changing

Stable

D changing

The above setup/hold diagram are for a falling-edge triggered FF. Setup/Hold times are not equal to each other, a typical specification might be Tsu = 3 ns, Thd = 1ns.

BR 8/99 10

Setup/Hold For JK FFtsu thd

C

J changing

Stable

J changing

K changing

Stable

K changing

Both J,K must satisfy setup/hold times

BR 8/99 11

Only Synchronous Inputs have Tsu,Thd

DQ

C

S

R

J

QC

S

R

K

S, R inputs are asynchronous inputs, no setup/hold times associated with them.

BR 8/99 12

What do you have to know?

• Difference between Synchronous, Asynchronous inputs on FFs

• Propagation delays for FF, Latches• Definition of Setup/Hold time