Bilinear design offully differential switched ...ims.unipv.it/~franco/JournalPaper/16.pdf ·...

Transcript of Bilinear design offully differential switched ...ims.unipv.it/~franco/JournalPaper/16.pdf ·...

Bilinear design of fully differentialswitched-capacitor ladder filters

Prof. F. Maloberti, Mem. I.E.E.E., A.E.I., Prof. F. Montecchi, Mem. I.E.E.E.,A.E.I., G. Torelli, Dr. Eng., and E. Halasz, Ph.D., Cand.Eng.Sci.

Indexing terms: Filters andfiltering, Circuit theory and design

Abstract: FulIy differential switched-eapacitor (SC) analogue blocks are shown to be suitable for implementingSC ladder filters via the bilinear transform of the corresponding analogue RLC passive prototypes. These filtersbecome fulIy insensitive to parasitic capacitance elfects, while the interesting features of the dilferential implementation, i.e. power supply and common mode rejection ratios and dynarnic range improvements, are retained.The technique presented is useful for the exact design of wide-band SC filters, i.e. for filters with a small ratiobetween the dock frequency and the cut-olf frequency. As an example, the bilinear design of an 8th-order Cauerbandpass filter is given, with numerically computed results.

(1)

(2)

1 Introduction

The most widely used technique for designing high-orderswitched-capacitor (SC) filters has been the one whichrefers to the flow-graph description of an analogue RLCpassive prototype, generally .considered as a doubly terminated LC lossless ladder chain [1]. This method followsthe technique ùsed in the past for the design of activeladder filters (active leapfrog structures) [2].

The active ladder configuration is current1y regarded asthe optimum choice for high-selectivity se filter design, asthe very low sensitivity of the passband response withrespect to the component variations [3] is retained in seimplementations as well as in the originaI passive prototype and in its continuous-time active realisations [4].

Presently, se implementations are derived from theflow-graph description by using the concept of the 'losslessdiscrete integrator' (LOI) [5], or, in other words, by usingthe LOI transformation, which relates the complex frequency variable S of the analogue prototype to thecomplex variable z of the sampled-data system, accordingto the following relationship:

1s- - (Zl /2 _ Z-1 /2)T

where T represents the sampling periodoThe LOI transformation works quite well so long as the

sampling frequency f. == l/T ismuch higher than thecut-off frequency fh' A ratio fJfh in the range of 30 to 50has generally been considered in classical implementationsfor the voice frequency range (PCM filters) [6].

Such a large ratio fJfh is required as the LOI transformation cannot be physically implemented in the terminatingsections of the ladder chain, where damped integrators areneeded to simulate the load and source resistors of theanalogue prototype [4]. This aspect is generally referred asthe 'termination error', because of the extra phase shift inthe damping loop of the actual damped SC integratbrswith respect to the required one [7].

To overcome this shortcoming, predistortion methodshave been used [8]. Alternative design techniques can be

Paper 4207G (E10), first received 15th January and in revised fonn 1st Augusti985Professors Maloberti and Montecchi are with the Dipartimento di Elettronica, Universita di Pavia, Corso Strada Nuova 106/c, 27100 Pavia, ltaly. Dr. Torelli is withSGS-Microelettronica, Agrate Brianza (MI), Italy. Dr. Hahisz is with the Institute ofTelecommunication & Electronics, Technical University of Budapesl,Stoczek u.2,Buda'pest H-I Il I, Hungary

266

followed to obtain the exact implementations [9-12]. IngeneraI, these techniques are quite cumbersome to use, andthe simplest satisfactory technique is the one that usesboth LOI and 'bilinear' transforms [13]. More recent1y,exact design methods of LOI structures have been given,referring to standard tables for wave digitaI filters [14].

In contrast to the LOI transformation, the bilinear s toz transformation,

2 z - 1s----Tz+l

can avoid any termination error when used for se ladderfilters, as its application can also be ex.tended for dampedintegrators. Frequency warping effects will be introduced,but their presence can easily be taken into account bymeans ofprewarping techniques [4].

Unfortunately, first-order se blocks bilinearly referredto their continuous-time active counterpart are parasiticsensitive [15] or, when not, they require equally valuedcapacitors or multiphase clocking schemes [16, 17].

A 'bilinear se resistor' could represent an optimum solution which combines the advantageous properties of boththe leapfrog circuit and the s to z bilinear mapping. Moreover, this is achieved by means of an immediate and easydesign of all the time constants of the flow-graph integrators [18].

In the present work, we show how the fully differentialstructure can be used to obtain positive and/or negativeSC resistors, so as to have available positive and/or negative parastitic insensitive bilinear integrators (both dampedand not damped), to be used as basic building blocks foran se leapfrog design.

The differential approach presented here is simpler thanthe alternative bilinear design technique of se ladderfilters given in Reference 19.

In Section 2, the basic bilinear se circuits are presented,in Section 3 the design procedure is given, ànd in Section 4the design of an 8th-order Cauer bandpass filter is shownas an example.

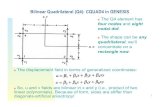

2 Bilinear differential integrators

The basic building blocks useful for implementing SCladder filters via flow-graph techniques are the first-orderintegrators, positive and negative, with or without a'resistive' damping. If the design implies transmissionzeros, the summing operation is also required, togetherwith the integration of other input signals.

IEE PROCEEDINGS, Vol. 132, Pt. G, No.6, DECEMBER 1985

(6a)

V:(z) - V;(z)H l (z) == ---":+....:.....:.._.........::.....:.....:..

Vin(z) - Vin(z)

(z + 1) Z(2iXCl + a + iX') - iX - iX'

= - (z - 1) z(2 + a + iX') - 2

If the positive and negative paths are well matched, i.e.iX = iX', we obtain

V:[(n + l)T] = V:(nT) ~ a{Vi~[(n+ 1)T] - Vi~(nT)}

+ (1 + a)Vx[(n + 1)T] - Vx(nT) (5a)

Vo-[(n + 1)T] = V;(nT) - a'{Vi~[(n + l)T] - Vi~(nT)}

+ (1 + a')Vx[(n + l)T] - VAnT) (5b)

with a = CdC2, a' = C'dC~ and Vx being the voltage ofthe virtual ground nodes.

Taking the z-transform of eqns. 5a and 5b, under theassumption that the inpilt signal has no common modeterm, we obtain

fully differential forrn by using a differential operationalamplifier of the type reported, for example, in Reference21; a common mode feedback internaI to the operationalamplifier ensures that at any instant Va+ = - V; .

The bilinear SC integrator of Fig. lC uses parasiticinsensitive SC structures, being each node of each capacitor switched between two voltage sources, or betweenground and virtual ground [20]. Assuming that the inputvoltages do not change for an overall sampling period T,we can write

(3)

ci

If a positive integrator is required, an inverter has to beadded. This is no longer necessary if a fully differentialimplementation is used, as shown in Fig. lB, where the

Fig. 1A Continuous-time active integrator

Fig. 1B Differential active integrator

In Fig. lA, the classical continuous-time active integrator is shown. Hs transfer function is given by:

Fig. 1 C Bilinear SC active integralOr

IEE PROCEEDINGS, Val. 132, Pt. G, No.6, DECEMBER 1985

(7)

(8)H (s) __ R3 __1__02 - R

11 + S R

3C

2

Fig.2A Continuous-time damped integrator

H(z) = _ Cl (z - 1) (6b)l C2 z + 1

A positive transfer function is obtained by reversing theinput connection as in the differential continuous-timecase.

Eqn. 6b can be recognised as being the transfer functionof a sampled-data bilinear integrator, which in turn can beregarded as having been derived from eqn. 30r eqn. 4b, bysubstituting s with the bilinear transibrm given in eqn. 2,using

Again, positive or negative integrators can be obtained inthe differential form, as shown in Fig. 2B, by simply controlling the proper connection of the input signal pair.

Following the same approach as far the lossless bilinear

267

TC --1- 2 R

l

and maintaining the integrating capacitor C2 at the samevalue as in the continuous time case. Such a bilinear SCintegrator has been independently considered by otherauthors [21].

In Fig. 2A, an active continuous-time damped integrator is shown.Its transfer function is given by

(4a)2 + S(L + L')

2s2,,' + S(L + L')

and L' = R'l C~. If now L' == L, eqn. 4awith L=R I C2becomes

operational amplifier can be, for example, of the type considered in Reference 25. Rere (Vi~' Vi~) represent the differential input signal pair, and (V: ,V0-) the differentialoutput signal pair. If the input signal has no commonmode terrns, i.e. V i~ = - V i~ , the transfer function of thestructure of Fig. 1B is given by

H ' () = V:(s) - V;(S)al S - + _

Vin(S) - Vin(S)

, 1Hal(s) = - -RC (4b)

s l 2

which is identical to eqn. 3.To obtain a positive integrator, the connection of the

input signal pair is reversed, whereas the output is takfmout with the same polarity as above. This is a natural consequence of the differential topology, where voltages ofboth polarity are available at each stage. Depending onthe connection between different stages, positive or negative transfer functions can be obtained.

In Fig. 1C, the bilinear SC integrator is shown in the

(11)

In se implementations, the substitution of R l and eventualIy also of R 3 with the equivalent bilinear sestructures,does not cause arìy mbdification in the transfer functionfrom v" to the output, as in any case

K - V: - V; _ - CA= V± - V+ - + C

x x 2

c;y.+ r/ Il, ,'"tnjG Cl • vg

/~--tl~

~

v. L- 1~I,g·

/~--ll~~t--Tc--l~

--t T I-Fig.4 Doubled-structure SC bilinear resistor

input of the operational amplifier work in turn in chargingand discharging phases during the same half clock period1;, = l/fc, thus doubling the actual sampling frequencyf. = l/T. In this case, T being the holding signal period,the correspondence between the doubled se structure andthe equivalent analogue resistor R l is given by

So, either positive or negative amplification gain constantsK are obtained, where the gain factor IK I is set by thecapacitive ratio CA/C2 ,

AlI the se integrators described above can be operatedat a sampling frequency equal to twice the clock frequencyfc if we duplicate the se structures and connect them asshown in Fig. 4. The two structures connected at the same

C2

C2

C3

~~T .... ........ TCp2 TCpl... ....

Bilinear SC damped integrator

C2

y i~ --c:::J-----,---t

C2

~ f,C p2 ,C pl

t ... ...T T

~'C3

R3

Fig.28 Differential damped integrator

given by

Fig.2e

integrator of Fig. le, the bilinear damped integrator(positive or negative) is obtained from the circuit of Fig.2e. The z-domain transfer function of this integrator is

R3

(10a)

(lOb)

(12)

(13)

3 Design of bilinear se ladder filters

, T TeCl = 2R

l= 4R

l

Similarly, damped integrators can be implemented.

As is welI known, the bilinear s to z transformation givenby eqn. 2 implies a warping effect between the continuoustime angular frequency n and the discrete-time angularfrequency w, given by

2 wTn =- tan--T 2

and no distortion error is associated with this transformation. This means that an equiripple analogue designretains its equipripple response, while the whole axis jnfrom - 00 to + 00 is mapped into the unit circle in thez-plane, according to the relationship z = eiroT

•

It is worthwhile noting that a zero is naturally introduced at the Nyquist frequency 1/2T for z = - l; this isan advantage of high-selectivity filter design over LDIbased design, where only the interval If I < l/nT ismapped onto the unit circle.

The warping effect can be disregarded in the range ofwT ~ l, as in this case n ~ w, and a continuous-time filterin the s-domain can be designed with exactly the samefinal specifications as required by the assigned mask.

Otherwise, if wT is not much smaller than unity, thewarping effect has to be taken into account and the desiredfinal mask has to be prewarped according to eqn. 13. 1f W i

are the characteristic frequencies of the filter to be

TC -

3 - 2R3

maintaining the integrating capacitor C2 at the same valueas in the continuous-time case.

The summing operation within an integrator can beperformed by means of capacitors, as illustrated in Fig. 3.

R3

Cl 1H 2(z) = - - (9)

C3 1 C2 Z - 1+--C3 z + 1

which can be regarded as derived from eqn. 8 using thebilinear s to z transform and by applying

TC -

l - 2Rl

R1

R3Fig.3 Positive or negative summing stage

268 IEE PROCEEDINGS, VoI. 132, Pt. G, No.6, DECEMBER 1985

designed, the analogue prototype must be chosen so as tomeet a mask, where the characteristic frequencies Oi areobtained as .

passband mask, but tilted up by the factor x/sin x withx = tan- 1 (0/1 MHz). Such a modified passband mask isshown in Fig. 7, where a}so the discretisation in narrow

(14)

Bandpass transformed prototype (denormalised values)

c~ = 0.477 JlFL; = 0.416 JlHc; = 4.579 JlFL~ = 2.292 JlHc~ = 0.831 JlFR I• = 0.9802 o

0.1095

0.4415Vin Vo

0.7693

0.353 I 10.8822 0.9802

Fig.5 Lowpass prototype

ciL2

VinRs L4

~voL"1.:2 Ci

l

rCi c31 RL

Fig.6

R = l oc; = 1.04 JlHc; = 1.832 JlFL; = 3.352 l,Hc; = 0.568 JlFL~ = 3.993 JlH

2 w·TO.=-tan-'-'T 2

Furthermore, when wT is not much smaller than unity,another effect is introduced by the se filter with respect tothe analogue prototype, that is the sin (wT/2)/(wT/2) distortion, caused by the inherent holding at the output stageof any se network. To take this effect into account, theanalogue prototype must be designed to have a frequencyresponse HljO) tilted-up by a factor x/sin x wherex = tan - l (OT/2). This can be done either by consideringthe effect by means of proper direct approximationmethods [22], or by optimising the final RLC networkobtained without the x/sin x distortion [23]. We havechosen the second approach in the example given in thefollowing Section.

When the final reference RLC prototype has beenobtained, the standard flow-graph rules are followed [1] toderive the ladder chain of integrators. Each integrator isthen implemented with the differential blocks considered inSection 2, with the integrating time constants Ti set as

(15)CI

T·=T-, 2Cç

where CI is the integrating capacitor and CI; is the capacitor value of the se structure., From a different point of view, this corresponds to anelement-to-element substitution of the resistive components Rj of the active continuous-time ladder, where thebilinear differential se structures (with Cç = T/2R;) areproper1y connected for obtaining positive or negative bilinear se resistors.

-S.4

-S.S

-S.6

-5.7

-5.8ID'O

modifieddesign

-5.9

flat subintervals is reported, as required for the computeroptimising design [23].

After the optimisation [23] we obtain the values of thecomponents shown in Fig. 8.

c'2Rs

Li

c

1"vin

L4

L'L2 C2

L'l c1 r3 3

269

131.6

Prototype with the final values after optimisation

C2 = 0.485 I,FL~ =0.393 JlHC~ = 4.579 JlFL. = 2.291 JlHc. = 0.831 JlFR L = 1.165 o

r"'''''"m ,.,,,,,,,,,,, , " ...".,"", " """."""l

frequency. KHz

Passband mask correccedfor the x/sin xfactor

101.0

inilial design

I_ U<<<UeOl « <UUUUll' un (u'u,« « « (un{««{(<tu, (((u_

-6.1

-6.0

-62

Fig.7

Fig.8Rs = IOL', = 1.01I JlHC, = 1.808 JlFL~ = 3.363 JlHC, = 0.568 JlFL, = 3.982 JlH

4 Example

The approach described above.is shown in this Section inan example. The specifications of the filter to be designedare as fol1ows:

Passband: F1 = 90 kHz; Fh = 110 kHzRipple: 0.2 dB max.Stopband: F s1 = 70 kHz; Fsh = 130 kHz; Attenuation:

35 dBSampling frequency l/T = 500 kHz

First, ali the corner frequencies of the specified mask haveto be prewarped according to eqn. 14, giving

F; = 101.0 kHz

F~ = 131.6 kHz

F~l = 74.9 kHz

F~h = 169.5 kHz

As a second step, we must choose the analogue RLCprototype. Using the classical lowpass to bandpass transformation, the normalised 10wpass LC ladder prototype e04-01-20 has been chosen. Such a filter has a passbandripple much lower than the required one; this is to preventeventual imperfections in the optimisation step. The circuitwith denormalised values is givenin Fig. 5.

By transforming the 10wpass network into the bandpassone, we obtain the doubly terminated LC topology shownin Fig. 6. This filter will show a flat passband between F;and F~. Then, as a third step, the values of the componentsmust be modified so that the filter can satisfy the same

IEE PROCEEDINGS, VoI. 132, Pt. G, No.6, DECEMBER 1985

By using signal flow-graph techniques, we describe theelectrical behaviour of the final,bandpass topology. First,we open the inductor loop [24] as well as the capacitiveloop, obtaining the circuit of Fig. 9. The flow-graph shown

RS v, L2 ~ V3 LI, Cl,

Vin 12 I:TL, C, C3 L3 RL

k, V3 : :k2V3 k3 V, :

Fig. 9 RLC prototype reduced with equivalent Thévenin networks

L'l LI = L~//L~ = 0.777 JlHk l =--- = 0.231 C Co Co 2 376 FL'l + L~ l = l + 2 =. Jl

C2 L 2 = 3.982 JlHk 2 =--- = 0.239 C2 = 0.485 JlF

C'l + C2 L 3 = L2I/L~ = 0.352 JlHCo Fk

3= __2_ = 0.11 C3 = C2+C~ = 5.147 Jl

C2+ C~ L 4 = 2.291 JlHL' C4 = 0.831 JlF

k4 = __3_ = 0.105 RL

= 1.165L2+ L~ Rs = l

-k"

-,. Vin ----..._--+----1

,Rs

-, -,Fig.10 Flow-graph corresponding to the circuit ofFig. 9

in Fig. lO corresponds to this modified circuit, where thetwo branches k2 and k3 realise the transmission zero pair.

Finally, by using thé blocks considered in Section 2, weobtain the circuit of Fig. Il, where symbolic blocks havebeen used for the sake of simplicity. Inverting se blocksare used for positive branches and vice versa for negativeones to take into account the sign inversion of the activeintegrators.

Each tirne constant is then set according to eqn. 15 or,setting alI the switched capacitors of unit value, the integrating capacitors are set according to eqn. 15. The capacitor values have been scaled for dynamic rangeconsiderations, following the classical method [19]; thepassband gain of the filter is consequently set at zero dB.

The capacitor values are summarised in Table 1: thefirst column reports the starting values, the second columnreports the values after the dynamic range optimisation,and the third column reports the values normalised tounity capacitance [19]. The total capacitance is 208.5 witha capacitor ratio spread of 1: 13.3.

12

'4

13t- --4-__0UT

""'-+.._--oV •

Fig.11 Final SC.bandpassfilter (schematical representation)

i

-O-

270 IEE PROCEEDINGS, Vol. 132, Pt. G, No.6, DECEMBER 1985

frequency . k Hz

a

1 JACOBS, G.M., ALLSTOT, DJ., BRODERSEN, R.W., and GRAY,P.R.: 'Design techniques for MOS switched capacitor ladder filters',IEEE Trans., 1978, CAS-25, (12), pp. 1014-1020

2 MARTIN, K., and SEDRA, A.S.: 'Designing leap-frog and SFG filterswith optimum dynamic range', Proc. IEEE, 65,1977, pp. 1210-1211

3 ORCHARD, HJ.: 'Inductorless filters', Electron. Lett, 1966, 2, pp.224-225

4 GHAUSI, M.S., and LAKER, K.R., (Eds). 'Modern fi1ter design'(Prentice Hall, NJ, USA, 1981)

5 BRUTON, L.T.: 'Low-sensitivity digitai ladder filters' IEEE Trans.,1975, CAS-22, (3), pp. 168-176

6 GREGORIAN, R., and NICHOLSON, W.K, jr: 'CMOS switchedcapacitor filters for a PCM voice CODEG', IEEE J. Solid-State Circuits, 1979, SC-14, (6), pp. 970-980

7 CHOI, T.C., and BRODERSEN, R.W.: 'Considerations for HighFrequency Switched-Capacitor Ladder Filters', IEEE Trans., 1980,CAS-27, (6), pp. 545-552

8 DAVIS, R.D., and TRICK, T.N.: 'Optimum design of lowpassswitched-capacitor ladder filters', ibid., 1980, CAS-27, (6), pp. 522-527

9 SCANLAN, S.O.: 'Analysis and synthesis or switched-capacitor statevariable filters', ibid., 1981, CAS-28, (2), pp. 85-93

lO BAHER, H., and SCANLAN, S.O.: 'Exact synthesis of bandpassswitched-capacitor LDI ladder filters', ibid., 1984, CAS-31, (4), pp.342-348

11 DATAR, R.B., and SEDRA, A.S.: 'Exact design of strays-insensitiveswitched-capacitor ladder filters', ibid., 1983, CAS-30, (12), pp.888-897

12 LIU, KS.K., TURNER, L.E., and BRUTON, L.T.: 'Exact synthesis orLDI and LDD ladder filters', ibid., 1984, CAS-31, (4), pp. 369-381

13 LEE, M.S., and CHANG, c.: 'Switched-capacitor filters using theLD1 and the bilinear transformations', ibid., 1981, CAS-28, (4), pp.265-270

14 TAYLOR, J.T., and MAVOR, 1.: 'Exact design or stray-insensitiveswitched-capacitor lowpass ladder filters from unit-element prototypes', Electron. Lett., 1984,20, pp. 665-667

15 TEMES, G.c., ORCHARD, HJ., and JAHANBEGLOO, M.:'Switched-capacitor filter design using the bilinear z-transform', IEEETrans., 1978, CAS-25, (12), pp. 1039-1044

16 VELAZQUEZ-RAMOS, J., STEPHENSON, F.w., RIAD, S.M., andRIAD, A.A.: 'High rrequency switched-capacitor ladder filters'. 14thSoutheastern Symp. on System Theory, 1982, Dig. or Techn. Papers,pp. 114-117

17 ERIKSSON, S., and AKHLAGHI, H.: 'Noninverting parasiticcompensated bilinear SC integrator with only one amplifier', Electron.Lett., 1983, 19, pp. 450-452

18 MONTECCHI, F., and MALOBERTI, F.: 'Switched-capacitorladder filters for high frequency applications via bilinear resistor modeling'. 26th Midwest Symp. on Circuits and Systems, 1983, Dig. ofTechn. Papers, pp. 445-447

19 LEE, M.S., TEMES, G.C., CHANG, c., and GHADERI, M.B.: 'Bilinear switched-capacitor ladder filters', IEEE Trans., 1981, CAS-28, (8),pp. 811-821

20 MARTIN, K.: 'Improved circuits for the realization of switchedcapacitor filters', ibid., 1980, CAS-27, (4), pp. 237-244

6 References

5 Acknowledgment

Work partially supported by the Italian National Councilof Research, CNR.

The transmission zeros are realised by the capacitors CA

and CB shown in the schematic of Fig. 11; their values areset by the amplification constants k2 and k3 given from theflow-graph of Fig. lO, according to eqn. 11.

The frequency response of the filter has been calculatedusing the SWITCAP [26] package and it is shown in Fig.12a, and the details of the passband are shown in Fig. 12b.Rere, the actual sampled-data transfer function of thecircuit evaluated into the unit circle in z-domain is represented by curve A. When the holding effect is also takeninto account (curve B), the frequency response of thedesigned filter in the passband is sufficient1y flat, andsatisfies the required design mask.

12011010090

1.21.00.80.60.40.2

~ 0.0 r---,!--;..-.--......-------'''----''''''';:---\----~ B-0.4-0.6-0.8-1.0-1.2 L......_"---__~ ~ -~ '-'-.......

80frequency. kHz

b

Fig.12 Passband response ofthe SC filter

a Whole responseb Details in the passband excluding (curve A), and including (curve B) the sin x/xeffect

For practical implementation, the circuit of Fig. 11 canbe optimised in terms of the switch count. Combining theactions of the switches incident at the same operationalamplifier, there are eight switches per operational amplifier; moreover, two additional toggles are required in theinput structure.

Table 1 : Capacitor values

Switched-capacitors

Cin 1 1 2C, 1 0.8785 1.75C2 1 2.1815 4.37C3 1 0.8785 6.89C4 1 3.2916 5.96C5 1 1 1C6 1 1 2C7 1 0.8785 1.59Cs 1 0.5515 1Cg 1 1 3.19

C'o 1 .05515 6Cll 1 2.7510 8.77

C'2 1 0.5515 1

C'3 1 0.4274 1.36

C'4 1 0.8929 1.79C'5 1 0.4274 1C'6 1.1650 0.4979 1C'7 0.2311 0.1275 1C,s 0.1046 0.0919 1

Integrating capacitors

Ci' 2.3764 2.0877 4.18C/2 0.7773 1.6957 13.3C/3 0.4850 1.5964 1.59C/4 3.9820 3.9820 7.22C /5 5.1474 2.8387 9.05CI6 0.3519 0.9680 10.53Cn 0.8313 0.7422 1.73CIS 2.2910 0.9791 1.96

Transmission zeros

CA 0.5684 0.3135 1Cs 0.5684 0.4993 1

IEE PROCEEDINGS, VoI. 132, Pt. G, No.6, DECEMBER 1985 271

, 21 SENDEROWICZ, D., DREYER, S.F., HUGGINS, J.M., RAHIM,C.F., and LABER, C.A.: 'A family of differential NMOS analog circuits for a PCM codec filter chip', IEEE J; Solid-State Circuits, 1982,SC.17, pp. 1014-1023

22 NAKHLA, M.S.: 'Approximation of lowpass filters with frequencydependent input gain characteristic', IEEE Trans., 1979, CAS-26, (3),pp. 198-202

23 HALASZ, E.: 'Design centering and tolerancing, consideringenvironmental effects via a new type minimax optimisation', IEEProc. G, Electron Circuits & Syst., 1982, 129, pp. 134-138

Franco Maloberti was born in Parma in1945. He received the Laurea degree inPhysics in 1968. Since 1969 he has beenwith the Department of Electronics of theUniversity of Pavia, where he is now anAssociate Professor. His research interestsinclude the design of analogue MOS integrated circuits and switched-capacitor circuits.

Federico Montecchi was born in Terni,Italy, in 1950. He received the Laureadegree in electronics engineering from theUniversity of Pavia in 1973. Since 1975 hehas been with the Department of Electronics of the Faculty of Engineering, University of Pavia, where he is now anAssociate Professor. His scientific interestswere previously concerned with the noisecharacterisation of semiconductor components and circuits, mainly CCD, while he

is now working in the area of switched-capacitor networks.

272

24 GREGORIAN, R., and FANG, S.c.: 'Ladder simulation SC fiIterswith inductor loops', Electron. Lett., 1981, 17, pp. 786-788

25 BANU, M., and TSIVIDIS, Y.: 'Fully integrated active Re filters inMOS technology', IEEE J. Solid-State Circuits, 1983, SC-lS, pp.644-651

20 FANG, S.c., TSIVIDIS, Y.P., and WING, O.: 'SWITCAP: aswitched-capacitor network analysis program-Part I and II', IEEECircuits & Syst. Mag., Sep. 1983, pp. 4-10, and ibid., Dec. 1983, pp.41-46

Guido Torelli was born in Rome, Italy, in1949. He graduated in Electronic Engineering in 1973 from the University of Pavia,where after graduating he worked for oneyear as a researcher in the Institute of Electronics. In 1974 he joined SGS, where hewas engaged as a design engineer in MOSICs Development Department. He is now aProject Leader in the field of MOS ICs forConsumer Market. His design interestranges both in digitaI and in analog cir-cuits.

Edith Halasz was born in Budapest,Hungary. She received a Diploma in electrical engineering from the Technical University of Budapest. Her research interestsare in the areas of network theory, optimisation methods and computer-aideddesign. She has been a consultant tovarious electronic industries in the areas ofCAD of LC filters, SC filters, equalizers andtolerance centering of LC filters. Shereceived the degree of Doctor Techn. from

the Technical University of Budapest in 1972, and the degree ofCandidate of Sciences in circuit theory from the HungarianAcademy of Sciences, Budapest in 1983. Dr Hahisz works for theTechnical University of Budapest in the Institute of Telecommunication and Electronics.

IEE PROCEEDINGS, Vol. 132, Pt. G, No.6, DECEMBER 1985