BER-optimal ADC for Serial Links - Rice...

Transcript of BER-optimal ADC for Serial Links - Rice...

ISSCC 2015 Student Research Preview

• Speaker Name: Yingyan Lin

• Co-authors: Min-Sun Keel, Adam Faust,

Aolin Xu, Naresh R. Shanbhag, Elyse

Rosenbaum, and Andrew Singer

• Advisor’s name: Naresh R. Shanbhag

• Affiliation: ECE, UIUC

• Contact information of the speaker:

• Degree currently working on, and

expected year of completion: PhD, 2017

• Research area/interests: analog and

mixed signal circuit design

Yingyan Lin, UIUC,

MS

1

BER-optimal ADC for Serial Links

ISSCC 2015 Student Research Preview

Please answer the following questions

Hardware has been fabricated: (yes, no) yes

The chip has been tested: (yes, no) yes

The chip is being fabricated but not tested yet: (tested,

not yet tested) tested

Simulations only: (yes, no) no

Technology used: 90nm LP CMOS

I will be a student at the time of the presentation next

February. (yes, no) yes

2

ISSCC 2015 Student Research Preview

Abstract (less than 150 words)

ADCs in serial links employ SNDR and ENOB as a

performance metric as these are standard metrics for generic

ADC design. This paper studies the use of information based

metrics such as bit-error-rate (BER) for ADC design in serial

links. A 4GS/s BER minimizing ADC for serial links in 90nm

LP CMOS is presented. By treating the ADC and the back-

end digital circuits as a composite detector and setting the

quantization thresholds of the ADC to minimize the BER, the

required ADC resolution is reduced. Measurement results

show the BER achieved by the 3-bit non-uniform ADC-based

receiver is lower by a factor of 105 and 107 as compared to

the 4-bit uniform and 3-bit uniform ADC-based receivers,

respectively, at a TX amplitude of 210 mVppd.

3

ISSCC 2015 Student Research Preview

Motivation & Problem Statement

Motivation & background of your research

- The emergence of ADC based multi-Gb/s serial link

receivers has enabled the application of digital signal

processing techniques to recover data under severe

channel impairments. A major impediment in ADC-

based receiver design is the implementation of the low

power and high-speed ADC.

Problem statement

- Explore low power ADC design for serial links

4

ISSCC 2015 Student Research Preview

Previous work by other groups

[1] showed that an adaptive minimum-BER equalizers outperform

conventional MMSE equalizers over a wide variety of channels. [2]

demonstrated the benefits of adapting the transmit and receive equalizer

coefficients, and the sampling phase of the CDR, to minimize the BER in

serial links. An ADC-based receiver was designed [3] using a low-gain

analog and mixed-mode pre-equalizer in conjunction with non-uniform

reference levels for the ADC. The work in [3] adjusts a pseudo-BER metric

(voltage margin) to minimize BER which in effect emulates an ADC with

BER-optimal reference levels. [4] proposed a power efficient equalizing

receiver front-end that includes a two-step adaptation BER minimizing

equalizer algorithm. These works demonstrate that the use of information-

based metrics such as the BER are indeed quite effective in reducing

power of link components in serial links.

5

ISSCC 2015 Student Research Preview

Previous Work from Your Group

[5] proposed BER-optimal ADC where quantization levels

and thresholds are set non-uniformly to minimize the BER.

And [6] extended the work in [5] with more general

theoretical analysis and simulation results.

However, the results in [5] and [6] were obtained under the

assumption that the ADC components were ideal, i.e., the

ADC consists of a sampler with infinite bandwidth and a

quantizer without metastability. Both the finite sampling

bandwidth and the metastability may affect the BER.

6

ISSCC 2015 Student Research Preview

Differentiate with you or your co-author’s previous publications

- This work studies the use of information based metrics

such as BER for ADC design in serial links, and design a

prototype IC to verify the benefits of the BER-optimal ADC-

based receiver on silicon.

If there are multiple authors*, what is YOUR contribution?

- I designed the 4GS/s ADC in the prototype IC, measured

the performance of the standalone ADC, and then took the

major responsibility to configure the ADC chip with the

backend FPGA to work as a BER-optimal ADC-based

receiver.

7

Contribution from You

ISSCC 2015 Student Research Preview

BER-optimal ADC Concept

Conventional ADC (fidelity criterion)

- Treated as a standalone component

- Designed as waveform preserver

BER-optimal ADC (detection criterion)

- ADC + digital equalizer + slicer

as a composite detector

- Adjust thresholds t, according to h and w,

to minimize BER

- 1-bit reduction of flash ADC → 50% power

savings (assuming ideal ADC model)

BE

R

SNR (dB)

( )n t

[ ]b nDriver

BackplaneChannel

noise

VGA ADC

CLKRecovery

DigitalEqualizer

Slicer

CLK

[̂ ]b n

t w

( )x t [ ]x n [ ]y n)(txc

8

ISSCC 2015 Student Research Preview

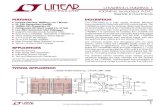

BER-optimal ADC for Serial Links

9

4-bit 4-GS/s Flash ADC,

IBM 90nm LP CMOS (1P 8M)

15 pre-amps, 3-stage metastability

latches, Gray-encoder

DAC controlled references, 3bit/4bit

configurable ADC mode

BER-optimal

ADCChannel

QL-UD

ENC

Slicer

F-block

Weightupdate

PRBSGen.

DataSync

Back-end FPGA

ADC chip

Composite detector

Clock distribution

ADC_IN+/-

Th

erm

om

ete

r-to

-B

ina

ry e

nc

od

er

Registerbank

Sto

rag

e c

ap

ac

ito

rSDISCI

Comparator array

DAC_CLK

8-bitDAC

CLK_IN+/-

OUT[3:0]

AD

Cc

ore

DAC

Sto

rag

ec

ap

RegisterBank

Clk

Chip microphotograph

ISSCC 2015 Student Research Preview

Link Test

3.93 3.93 3.62 3.58

3.4

0

1

2

3

4

5

0 0.5 1 1.5 2

AD

C E

NO

B [

bit

s]

ADC input frequency [GHz]

Stand-alone 4b ADC measurement results

- Power consumption: 59.7 mW (ADC core only)

- FOM = 1.42 pJ/conv.-step (ADC core only)

Measured ADC Performance Link Test Environment

BERT

ADC

board

CLK+

CLK-

ADC+ ADC-

OUT[3:0]

SCI/SDI

FPGA

board

Channel

BERT

ADC

board

CLK+

CLK-

ADC+ ADC-

OUT[3:0]

SCI/SDI

FPGA

board

Channel

Channel Board

ADC PCB

FPGA Board

BERT

10

ISSCC 2015 Student Research Preview 11

Measured ADC ENOB vs. input frequency and BER vs. TX amplitude at

4-Gb/s when ADC FSR is 100 mVppd.

1.E-12

1.E-10

1.E-08

1.E-06

1.E-04

1.E-02

170 190 210 230

BE

R

TX amplitude [mVppd]

3b unif

4b unif

3b nonunif 30mVppd

105

0

1

2

3

0.5 1 1.5 2

EN

OB

[bit

s]

fin[GHz]

4b unif3bunif3b nonunif

ENOB vs. input freq. BER vs. TX amplitude

ADC ENOBs and Link BERs

ENOB is not the right metric for designing ADCs for serial links

BER achieved by the 3-bit BER optimal ADC-based receiver is

lower by a factor of 105, as compared to the 4-bit uniform ADC-

based receiver.

ISSCC 2015 Student Research Preview 12

Comparison Table

This work achieves the lowest BER (< 10-12) with a 3-bit resolution and better

energy efficiency than ADC-based receivers [7], [8], [9] based on comparable

technologies.

Thiswork

JSSCC12[3]

ISSCC09[7]

ISSCC11[8]

ISSCC08[9]

Process 90-nm LP 65-nm 65-nm 65-nm 90-nm

Data Rate [Gb/s] 4 10 10.3 5 10.3

Number of bits 3 3 6 5 8

BER @channel< 1E-12@20”

< 1E-7@-17dB

< 1E-15@-26dB

< 1E-12@34”

N/A

RX power [mW] 60.7/86 106 500 192 1600

RX efficiency [pJ/bit] *15.2/*21.5 10.6 48.5 38.4 155.3

ADC operating mode 3b non-uniform 4b uniform

Technology 90-nm LP CMOS (1P8M)

Core die area 0.38 mm2

Supply voltage 1.2V for analog, 1.28V for digital & clock

Data rate 4 Gb/s

Power

consumption

ADC (FOM) 30.7 mW 59.7 mW

B/E digital *30 mW *28 mW

* Digital back-end power estimated from synthesis in 90-nm LP CMOS

ISSCC 2015 Student Research Preview

References [1] C.-C. Yeh and J. Barry, “Adaptive minimum bit-error rate equalization for binary signaling,” IEEE

Transactions on Communication, vol. 48, no. 7, pp. 1226–1235, Jul 2000.

[2] E.-H. Chen, W. Leven, N. Warke, A. Joy, S. Hubbins, A. Amerasekera, and C.-K. Yang, “Adaptation of

CDR and full scale range of ADC-based SerDes receiver,” in 2009 Symposium on VLSI Circuits, June

2009, pp. 12–13.

[3] E. Chen, et al., “10 Gb/s serial I/O receiver based on variable ADC,” IEEE Symp. VLSI Circuits, pp.

288-289, 2011.

[4] S. Son, H.-S. Kim, M.-J. Park, K. Kim, E.-H. Chen, B. Leibowitz, and J. Kim, “A 2.3-mW, 5-Gb/s low-

power decision-feedback equalizer receiver front-end and its two-step, minimum bit-error-rate adaptation

algorithm,” IEEE Journal of Solid-State Circuits, vol. 48, no. 11, pp. 2693–2704, Nov 2013.

[5] M. Lu, N. Shanbhag, and A. Singer, “BER-optimal analog-to-digital converters for communication links,”

in Proceedings of 2010 IEEE International Symposium on Circuits and Systems (ISCAS), May 2010, pp.

1029–1032.

[6] R. Narasimha, M. Lu, N. Shanbhag, and A. Singer, “Ber-optimal analogto-digital converters for

communication links,” IEEE Transactions on Signal Processing, vol. 60, no. 7, pp. 3683–3691, July 2012.

[7] J. Cao, et al., “A 500mW digitally calibrated AFE in 65nm CMOS for 10Gb/s serial links over backplane

and multimode fiber,” ISSCC Dig. Tech. Papers, pp. 370-371,371a, 2009.

[8] B. Abiri. et al., “A 5Gb/s Adaptive DFE for 2× Blind ADC-Based CDR in 65nm CMOS,” ISSCC Dig.

Tech. Papers, pp. 436-438, 2011.

[9] O. Agazzi, D. Crivelli, M. Hueda, et al., “A 90nm CMOS DSP MLSD Transceiver with Integrated AFE

for Electronic Dispersion Compensation of Multi-mode Optical Fibers at 10Gb/s,” ISSCC Dig. Tech.

Papers, pp. 232-233, 2008.

13