November 1, 2015ICS102: Expressions & Assignment 1 Expressions and Assignment.

Assignment 1

-

Upload

pokcikhensem -

Category

Documents

-

view

385 -

download

1

Transcript of Assignment 1

UNIVERSITI TUN HUSSEIN ONN MALAYSIA (UTHM) FACULTY OF ELECTRICAL AND ELECTRONIC ENGINEERING

ASSIGNMENT 1 (PART B – QUESTION NO.3)

UPDATED REPORT ON 24/10/2012

by:-

1) MUHAMMAD NUR HIDAYAT BIN ZAHARI (GE 120073)

2) NORYATI BINTI MOHAMED SAPARI (HE 110189)

(MEE – SEM I 2012/2013)

Lecturer: Dr. Mohd Shamian Bin Zainal

PROGRAMMABLE ELECTRONIC (MEE 10203)

MUHAMMAD NUR HIDAYAT BIN ZAHARI GE 120073 NORYATI BINTI MOHAMED SAPARI HE 110189

2/12

MEE10203 Programmable Electronic

Assignment 1 (Part B)

Questions and Answers:-

Write a Word document discussing the following projects. Submit supporting VHDL projects

code. Demonstrate the working projects to the instructor (and class). If you are not able to

complete this assignment by the due date, submit a progress report documenting your work to

that time.

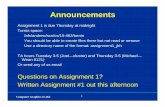

3. Design and implement a DE2/DE1 project that generates simulated quadrature encoder

pulses. Use SW [15:0] to set the quarter-period. Use the GPIO pins for the output. Use

SW3 to change direction. In one direction, the pulse sequence is 00, 01, 11, 10. In the

other direction the pulse sequence is 00, 10, 11, 01. (2012/10/17)

Answer:-

Additional information and correction of first report submission dated 17 October

2012 (17/10/2012).

i) Correction on VHDL description for simulated quadrature encoder pulses.

The VHDL codes for this simulated quadrature encoder pulses were done

impartially and connected with each other by using block diagram layout method

as shown in schematic layout as per Figure 1 below.

VCCsw3 INPUT

VCCClk INPUT

Z[1..0]OUTPUT

Clk Z[1..0]

quadrature

inst

sw3

A[1..0]

Z[1..0]

quar

inst2

50Mhz 5Mhz

500khz

50khz

5khz

500hz

50hz

5hz

blockclk

inst3

GND

Figure 1: Schematic Layout for Simulated Quadrature Encoder Pulses

MUHAMMAD NUR HIDAYAT BIN ZAHARI GE 120073 NORYATI BINTI MOHAMED SAPARI HE 110189

3/12

The VHDL descriptions for each block segment as layout in the schematic

diagram are as follows:-

a) VHDL description for 1st block segment which is the 'block clk' are as follow:-

library ieee ;

use ieee.std_logic_1164.all ;

entity clk is

port (

CLKIN : in std_logic;

CLKOUT : out std_logic

);

end clk;

architecture behavioral of clk is

begin

process (CLKIN)

variable CNT1: integer range 0 to 4;

variable CNT2: std_logic;

begin

if (CLKIN'event and CLKIN='1') then

if (CNT1=4) then

CNT1 := 0;

CNT2 := not CNT2;

else CNT1 := CNT1 +1;

end if;

end if;

CLKOUT <= CNT2;

end process;

end behavioral;

b) VHDL description for 2nd block segment which is the 'quadrature' are as

follow:-

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity quadrature is

Port (

Clk : in STD_LOGIC;

MUHAMMAD NUR HIDAYAT BIN ZAHARI GE 120073 NORYATI BINTI MOHAMED SAPARI HE 110189

4/12

Z: out STD_LOGIC_VECTOR (1 downto 0));

end quadrature;

architecture Behaviour of quadrature is

signal output: STD_LOGIC_VECTOR (1 downto 0);

begin

process (Clk)

begin

if (Clk'event and Clk='1') then

case output is

when "00" => output <= "10";

when "01" => output <= "11";

when "10" => output <= "01";

when others => output <= "00";

end case;

end if;

end process;

Z(1)<=output(1);

Z(0)<=output(0);

end Behaviour;

c) VHDL description for 3rd block segment which is the 'quar' are as follow:-

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity quar is

port(

sw3: in bit;

A:in std_logic_vector (1 downto 0);

Z: out std_logic_vector (1 downto 0));

end quar;

architecture code of quar is

signal output:std_logic_vector(1 downto 0);

begin

process (sw3)

begin

case sw3 is

when '1'=>

output(0)<= (A(1) and not A(0)) or (not A(1) and A(0));

output(1)<=A(1);

MUHAMMAD NUR HIDAYAT BIN ZAHARI GE 120073 NORYATI BINTI MOHAMED SAPARI HE 110189

5/12

when '0'=>

output(0)<=A(1);

output(1)<=((A(1) and not A(0)) or (not A(1) and A(0)));

when others => null;

end case;

end process;

Z<=output;

end code;

ii) Compilation successful result:-

Figure 2: Successful Compilation Result Pop-up Window

MUHAMMAD NUR HIDAYAT BIN ZAHARI GE 120073 NORYATI BINTI MOHAMED SAPARI HE 110189

6/12

iii) Vector waveform file (.vwf) generation result by FUNCTIONAL simulation.

Figure 3a: Full View of the Vector Waveform Generation

Figure 3b: Zoom-in of the Vector Waveform Generation

When direction switch of SW3 change, the output signal shows toggle changes correspond to the input switches.

When direction switch of SW3 change, the output signals [Z(0)Z(1)] logic combination shows toggle changes from [00, 01, 11, 10] to [00, 10, 11, 01].

MUHAMMAD NUR HIDAYAT BIN ZAHARI GE 120073 NORYATI BINTI MOHAMED SAPARI HE 110189

7/12

From Figure 2, it has been shown that the compilation of the simulated

quadrature encoder pulses block diagram file (*.bdf) were successful with no error but

only had 14 warnings messages from the Quartus II compiler.

From Figure 3a and Figure 3b for waveform generation, it can be seen that the

generation of the output signals were success through simulator module in the Quartus II

software.

In the output waveform from Figure 3b, it can be seen that when the direction

switch of SW3 change, the output signals [Z(0)Z(1)] logic combination shows toggle

changes from [00, 01, 11, 10] to [00, 10, 11, 01] and thus fulfilled the design requirements

of the simulated quadrature encoder pulses as per question 3 Part B.

MUHAMMAD NUR HIDAYAT BIN ZAHARI GE 120073 NORYATI BINTI MOHAMED SAPARI HE 110189

8/12

iv) Hardware Testing on Altera DE2 Board and Output Waveform via Oscilloscope.

Hardware testing with Altera DE2 board were manage to be carried out on

17/10/2012 and the output waveform has been viewed through DSO3152A Digital

Storage Oscilloscope brand Agilent Technologies via two GPIO pins (Pin_E25 and

Pin_E26) for Channel A (Z0) and Channel B (Z1) from the Altera DE2 board.

The output waveform captured and viewed by the oscilloscope were then

channel and stored into personal computer via Agilent 3000 series oscilloscope

software and further edited for report attachment as presented below.

a) Pictures for test run the source code from item (i) above onto Altera DE2

Board and viewed the simulated quadrature encoder pulses through

oscilloscope.

Picture 1: Hardware Testing on Altera DE2 Board with

Oscilloscope Connection

MUHAMMAD NUR HIDAYAT BIN ZAHARI GE 120073 NORYATI BINTI MOHAMED SAPARI HE 110189

9/12

b) Hardware Setup onto Altera DE2 Board.

Picture 2: Hardware Testing Setup on Altera DE2 Board

c) GPIO Pins Connection.

Picture 3: GPIO Pin Connection on Altera DE2 Board

MUHAMMAD NUR HIDAYAT BIN ZAHARI GE 120073 NORYATI BINTI MOHAMED SAPARI HE 110189

10/12

d) Output waveform captured by the oscilloscope and further captured and

stored in the personal computer via Agilent 3000 series oscilloscope software.

i. Waveform for Channel A and Channel B without any change of direction

input data from switch SW3.

Figure 4a: Channel A and Channel B Output without Changes in SW3

Viewed via Agilent Oscilloscope

(Edited via Agilent 3000 Series Oscilloscope Software)

From Figure 4a above, it can be seen through the red box highlighted that

the Channel A and Channel B which viewed by the oscilloscope as Channel 1 and

Channel 2 respectively has shown logic combination of [00, 01, 11, 10] which

represent the simulated quadrature encoder pulses generated by the Altera DE2

board through GPIO pins and thus has fulfilled the design requirements as per

question 3 Part B.

MUHAMMAD NUR HIDAYAT BIN ZAHARI GE 120073 NORYATI BINTI MOHAMED SAPARI HE 110189

11/12

ii. Waveform for Channel A and Channel B with change of direction input data

from switch SW3.

Figure 4b: Channel A and Channel B Output with Changes in SW3

Viewed via Agilent Oscilloscope

(Edited via Agilent 3000 Series Oscilloscope Software)

From Figure 4b above, it can be seen through the red box highlighted that

the Channel A and Channel B which viewed by the oscilloscope as Channel 1 and

Channel 2 respectively has shown logic combination of [11, 01, 00, 10] which

represent the simulated quadrature encoder pulses generated by the Altera DE2

board through GPIO pins when there is an instruction of change of direction via

SW3 input data.

We can prove this by looking back to the original logic combination of

Channel A and Channel B from Figure 4a above which is [00, 01, 11, 10] and when

there is an input from switch SW3 at point of logic combination of [01] for

changing the direction of the quadrature rotation, the rotation changed and

produced [11, 01, 00, 10] logic combination to reflect to the switch SW3 input

instruction and thus has prove and fulfilled the design requirements as per

question 3 Part B.

MUHAMMAD NUR HIDAYAT BIN ZAHARI GE 120073 NORYATI BINTI MOHAMED SAPARI HE 110189

12/12

Conclusion:-

These reports present the answer for Question 3 Part B of Assignment 1 of Programmable

Electronic subject.

Here, we can conclude that the answer presented has fulfilled the design required in the

question 3 Part B which has been prove through hardware testing and output viewing via

oscilloscope.

References:-

1. Embedded SoPC Design With NIOS II Processor And VHDL Examples, Pong P. Chu, Wiley,

2011

2. http://www.ti.com/lit/ug/sprufl4a/sprufl4a.pdf