Advanced VLSI Design Unit 04: Combinational and Sequential Circuits.

-

Upload

john-gallagher -

Category

Documents

-

view

215 -

download

0

Transcript of Advanced VLSI Design Unit 04: Combinational and Sequential Circuits.

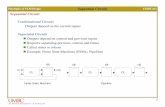

Advanced VLSI Design

Unit 04: Combinational and Sequential Circuits

Slide 2

Outline Basic CMOS Circuits Combinational Circuits Sequential Circuits

Slide 3

Transistors as Switches We can view MOS transistors as electrically

controlled switches Voltage at gate controls path from source to drain

g

s

d

g = 0

s

d

g = 1

s

d

g

s

d

s

d

s

d

nMOS

pMOS

OFF ON

ON OFF

Slide 4

CMOS Inverter

A Y

0

1

VDD

A Y

GNDA Y

Slide 5

Inverter Cross-section Typically use p-type substrate for nMOS transistors Requires n-well for body of pMOS transistors

n+

p substrate

p+

n well

A

YGND VDD

n+ p+

SiO2

n+ diffusion

p+ diffusion

polysilicon

metal1

nMOS transistor pMOS transistor

Slide 6

Inverter Mask Set Transistors and wires are defined by masks Cross-section taken along dashed line

GND VDD

Y

A

substrate tap well tapnMOS transistor pMOS transistor

Slide 7

Complementary CMOS Complementary CMOS logic gates

– nMOS pull-down network– pMOS pull-up network– a.k.a. static CMOS

pMOSpull-upnetwork

outputinputs

nMOSpull-downnetwork

Pull-up OFF Pull-up ON

Pull-down OFF Z (float) 1

Pull-down ON 0 X (crowbar)

Slide 8

Gate Layout Layout can be very time consuming

– Design gates to fit together nicely– Build a library of standard cells

Standard cell design methodology

– VDD and GND should abut (standard height)

– Adjacent gates should satisfy design rules– nMOS at bottom and pMOS at top– All gates include well and substrate contacts

Slide 9

Example: NAND3 Horizontal N-diffusion and p-diffusion strips Vertical polysilicon gates Metal1 VDD rail at top

Metal1 GND rail at bottom 32 by 40

Slide 10

Pseudo-nMOS In the old days, nMOS processes had no pMOS

– Instead, use pull-up transistor that is always ON In CMOS, use a pMOS that is always ON

– Ratio issue– Make pMOS about ¼ effective strength of

pulldown network

Vout

Vin

16/2

P/2

Ids

load

0 0.3 0.6 0.9 1.2 1.5 1.8

0

0.3

0.6

0.9

1.2

1.5

1.8

P = 24

P = 4

P = 14

Vin

Vout

Slide 11

Dynamic Logic Dynamic gates uses a clocked pMOS pullup Two modes: precharge and evaluate

1

2A Y

4/3

2/3

AY

1

1

AY

Static Pseudo-nMOS Dynamic

Precharge Evaluate

Y

Precharge

Slide 12

The Foot What if pulldown network is ON during precharge? Use series evaluation transistor to prevent fight.

AY

foot

precharge transistor

Y

inputs

Y

inputs

footed unfooted

f f

Slide 13

Monotonicity Dynamic gates require monotonically rising inputs

during evaluation– 0 -> 0– 0 -> 1– 1 -> 1– But not 1 -> 0

Precharge Evaluate

Y

Precharge

A

Output should rise but does not

violates monotonicity during evaluation

A

Slide 14

Domino Gates Follow dynamic stage with inverting static gate

– Dynamic / static pair is called domino gate– Produces monotonic outputs

Precharge Evaluate

W

Precharge

X

Y

Z

A

BC

C

AB

W XY Z =

XZH H

A

W

B C

X Y Z

domino AND

dynamicNAND

staticinverter

Slide 15

Pass Transistor Circuits Use pass transistors like switches to do logic Inputs drive diffusion terminals as well as gates

CMOS + Transmission Gates:– 2-input multiplexer– Gates should be restoring

A

B

S

S

S

Y

A

B

S

S

S

Y

Slide 16

Sequencing Combinational logic

– output depends on current inputs Sequential logic

– output depends on current and previous inputs– Requires separating previous, current, future– Called state– Ex: FSM, pipeline

CL

clk

in out

clk clk clk

CL CL

PipelineFinite State Machine

Slide 17

Sequencing Elements Latch: Level sensitive

– a.k.a. transparent latch, D latch Flip-flop: edge triggered

– A.k.a. master-slave flip-flop, D flip-flop, D register

D

Flo

p

Latc

h

Q

clk clk

D Q

clk

D

Q (latch)

Q (flop)

Slide 18

Latch Design Buffered output

+ No backdriving

Widely used in standard cells

+ Very robust (most important)- Rather large- Rather slow- High clock loading

Q

D X

Slide 19

Sequencing Methods Flip-flops 2-Phase Latches Pulsed Latches

Flip-F

lopsF

lop

Latc

h

Flo

p

clk

1

2

p

clk clk

Latc

h

Latc

h

p p

1 12

2-Phase T

ransparent LatchesP

ulsed Latches

Combinational Logic

CombinationalLogic

CombinationalLogic

Combinational Logic

Latc

h

Latc

h

Tc

Tc/2

tnonoverlap tnonoverlap

tpw

Half-Cycle 1 Half-Cycle 1

Slide 20

Clocking Summarized Flip-Flops:

– Very easy to use, supported by all tools 2-Phase Transparent Latches:

– Lots of skew tolerance and time borrowing Pulsed Latches:

– Fast, hold time risk