d9b54x484lq62.cloudfront.net · Created Date: 11/23/2015 4:43:43 PM

3 ( 35 + 4 + 4 = 43 points) 40 min.ee457_MT_Sp2012.fm March 30, 2012 3:16 pm EE457 Midterm Exam -...

Transcript of 3 ( 35 + 4 + 4 = 43 points) 40 min.ee457_MT_Sp2012.fm March 30, 2012 3:16 pm EE457 Midterm Exam -...

ee457_MT_Sp2012.fm

March 30, 2012 3:16 pm EE457 Midterm Exam - Spring 2012 Page - 8 / 8 C Copyright 2012 Gandhi Puvvada

3 ( 35 + 4 + 4 = 43 points) 40 min.

Virtual Memory:

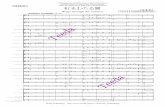

3.1 A 32-entry 2-way set-associative TLB contents (in hex) are given on the side. In this virtual memory system, 64KB pages are used. The processor is a 32-bit logical address 64-bit data byte addressable processor. 1. Divide the Virtual Address into VPN and Page offset fields. Divide the VPN further into Tag and Set fields.

Similarly divide the Physical Address into PPFN and Page offset fields.

2. To make sure that I did not fill random VPNs, which can potentially make up a meaningless TLB content, I should ____________________________________________________________________________________________________________________________________________Similarly, to make sure that I did not fill random PPFNs, which can potentially make up a meaningless TLB content, I should __________________________________________________________________________________________________________________________________3. If the TLB is all empty to start with, translation for how many consecutive virtual pages we can hold in the TLB? ___________. If we are unlucky, how early can we get conflict, requiring replacement in TLB? _____________________________________________________________ 4. Based on the TLB contents, arrive at the following:Number of valid entries in the TLB _____________. List all those valid VPNs for which we have translation here: _________________________________________________________________Translations for two consecutive Virtual pages ____________ (always / never / sometimes) go into the two entries of a set.Are there any consecutive (valid) VPNs? _____ (Y / N). If Yes, list them here: ________________ 5. How many comparators of what size are used in this TLB? _____________________________________________________________________________________________________________

3.2 Since we use write-back only for virtual memory, we need to maintain a dirty bit associated with ________________________________________________ (the entire TLB /the entire Page Table / each entry of the page table / each entry of the TLB / each entry in both TLB and Page Table).

3.3 Fully associative mapping may not be prohibitively expensive in the case of a _________________(TLB / L2 cache) because __________________________________________________________________________________________________________________________________________

v v1 0 0 1 0 1 2 3 Set #0 1 1 1 2 1 2 3 40 5 6 7 4 4 4 4 Set #1 0 6 7 8 4 4 4 40 8 9 A 4 4 4 4 Set #2 0 9 A B 4 4 4 40 B C D 4 4 4 4 Set #3 0 C D E 4 4 4 40 E F 0 4 4 4 4 Set #4 0 F 0 1 4 4 4 40 1 1 1 4 4 4 4 Set #5 0 2 2 2 4 4 4 40 2 2 2 4 4 4 4 Set #6 0 3 3 3 4 4 4 40 3 3 3 4 4 4 4 Set #7 0 4 4 4 4 4 4 40 4 4 4 4 4 4 4 Set #8 0 5 5 5 4 4 4 40 5 5 5 4 4 4 4 Set #9 1 6 6 6 6 7 8 90 6 6 6 4 4 4 4 Set #A 0 7 7 7 4 4 4 41 7 8 9 5 6 7 8 Set #B 0 8 9 A 4 4 4 40 A B C 4 4 4 4 Set #C 0 B C D 4 4 4 40 D E F 4 4 4 4 Set #D 0 E F 0 4 4 4 41 0 0 0 7 8 9 A Set #E 1 1 1 1 8 9 A B0 0 0 0 4 4 4 4 Set #F 1 0 0 0 9 A B C

TAG TAGPPFN PPFN

2pts

VA31 VA[2:0]

1pts

PA31 PA[2:0]

10pts

4pts

14pts

4pts

4pts

4pts

The next few weeks are very important as we will be covering a lot of material in 4 weeks. Please, do attend every lecture and discussion. And use our office hours. Thanks. -- The EE457 Teaching Team

ee457_MT_Sp2012.fm

March 30, 2012 5:37 am EE457 Midterm Exam - Spring 2012 Page - 8 / 8 C Copyright 2012 Gandhi Puvvada

3 ( 35 + 4 + 4 = 43 points) 30 min.

Virtual Memory:

3.1 A 32-entry 2-way set-associative TLB contents (in hex) are given on the side. In this virtual memory system, 64KB pages are used. The processor is a 32-bit logical address 64-bit data byte addressable processor. 1. Divide the Virtual Address into VPN and Page offset fields. Divide the VPN further into Tag and Set fields.

Similarly divide the Physical Address into PPFN and Page offset fields.

2. To make sure that I did not fill random VPNs, which can potentially make up a meaningless TLB content, I should ____________________________________________________________________________________________________________________________________________Similarly, to make sure that I did not fill random PPFNs, which can potentially make up a meaningless TLB content, I should __________________________________________________________________________________________________________________________________3. If the TLB is all empty to start with, translation for how many consecutive virtual pages we can hold in the TLB? ___________. If we are unlucky, how early can we get conflict, requiring replacement in TLB? _____________________________________________________________ 4. Based on the TLB contents, arrive at the following:Number of valid entries in the TLB _____________. List all those valid VPNs for which we have translation here: _________________________________________________________________Translations for two consecutive Virtual pages ____________ (always / never / sometimes) go into the two entries of a set.Are there any consecutive (valid) VPNs? _____ (Y / N). If Yes, list them here: ________________ 5. How many comparators of what size are used in this TLB? _____________________________________________________________________________________________________________

3.2 Since we use write-back only for virtual memory, we need to maintain a dirty bit associated with ________________________________________________ (the entire TLB /the entire Page Table / each entry of the page table / each entry of the TLB / each entry in both TLB and Page Table).

3.3 Fully associative mapping may not be prohibitively expensive in the case of a _________________(TLB / L2 cache) because __________________________________________________________________________________________________________________________________________

v v1 0 0 1 0 1 2 3 Set #0 1 1 1 2 1 2 3 40 5 6 7 4 4 4 4 Set #1 0 6 7 8 4 4 4 40 8 9 A 4 4 4 4 Set #2 0 9 A B 4 4 4 40 B C D 4 4 4 4 Set #3 0 C D E 4 4 4 40 E F 0 4 4 4 4 Set #4 0 F 0 1 4 4 4 40 1 1 1 4 4 4 4 Set #5 0 2 2 2 4 4 4 40 2 2 2 4 4 4 4 Set #6 0 3 3 3 4 4 4 40 3 3 3 4 4 4 4 Set #7 0 4 4 4 4 4 4 40 4 4 4 4 4 4 4 Set #8 0 5 5 5 4 4 4 40 5 5 5 4 4 4 4 Set #9 1 6 6 6 6 7 8 90 6 6 6 4 4 4 4 Set #A 0 7 7 7 4 4 4 41 7 8 9 5 6 7 8 Set #B 0 8 9 A 4 4 4 40 A B C 4 4 4 4 Set #C 0 B C D 4 4 4 40 D E F 4 4 4 4 Set #D 0 E F 0 4 4 4 41 0 0 0 7 8 9 A Set #E 1 1 1 1 8 9 A B0 0 0 0 4 4 4 4 Set #F 1 0 0 0 9 A B C

TAG TAGPPFN PPFN

2pts

VA31 VA[2:0]

1pts

PA31 PA[2:0]

10pts

4pts

14pts

4pts

4pts

4pts

The next few weeks are very important as we will be covering a lot of material in 4 weeks. Please, do attend every lecture and discussion. And use our office hours. Thanks. -- The EE457 Teaching Team