2010 International Electrostatic Discharge Workshop - ESD A · Co-Sponsored by You are cordially...

Transcript of 2010 International Electrostatic Discharge Workshop - ESD A · Co-Sponsored by You are cordially...

www.esda.orgCo-Sponsored by

You are cordially invited to participate in the 2010 International ESD Workshop. The IEW provides a unique environment for envisioning, developing, and sharing ESD design and test technology for present and future semiconductor applications. Here you will closely interact with your peers at technical sessions, moderated discussion groups, poster sessions, seminars, and special interest groups.

This workshop happens in a time of an important paradigm shift in ESD robustness design. Constraints of modern technologies and performance requirements restrict the ability to design practical overall ESD robustness on-chip. At the same time, system ESD requirements have become more demanding. IEW 2010 provides the chance of better alignment between system manufacturers and IC suppliers by discussion and exchange in a relaxed atmosphere of interactive learning. This workshop should be equally beneficial for IC and system ESD designers.

Located on the shores of Lake Starnberg, 40 kilometers southwest of Munich, lies the Tutzing estate and its 18th century mansion. With its modern conference rooms and facilities, this venue is well suited for the workshop. The on-site single and double bedrooms provide a comfortable stay within the quietness of the private park around the castle. From the balconies and the patios there is a magnificent view of the Bavarian Alps. The spirit of this place encourages thoughtful discussion and intensive interaction.

Come and be inspired!

IEWMay 10-13, 2010 Evangelische Akademie, Tutzing, Germany

IEW2010 International Electrostatic

Discharge Workshop2010 International Electrostatic

Discharge Workshop

�

IEWFor the latest information on this and other IEW topics visit: http://www.esda.org/IEW.htmIEW - An Interactive Experience

A primary goal of the International ESD Workshop is to encourage extensive interaction among attendees, speakers, and organizing committees. The oral and poster presentations in the 2010 technical program are considered of equal value and importance. However, emphasis is being placed on poster presentations, which fit very well in the interactive environment of the workshop. As in the past, oral presentations will be 20 minutes in length with an additional 5 minutes allotted for questions and answers. Each invited poster author will present a 5 minute oral summary of their work in addition to hosting their poster in the poster session mixers.

Four discussion groups are planned, covering a variety of relevant and interesting ESD topics. Here questions can be asked, new ideas can be proposed and refined, and conventional wisdom can be tested. This year’s workshop adds a Tuesday evening fireside talk summarizing the interesting experiences of the Industry Council.

Special interest groups (SIG) provide an opportunity for engineers with similar concerns to look for solutions to their common problems. Five SIG topics are already planned and attendees are encouraged to form new SIGs during the workshop.

Come and share your views, give your inputs, ask your questions, network with experts from industry, and above all learn something new in an informal, interactive, and constructive atmosphere.

Management Committee:

Technical Program Chair: Gaudenzio Meneghesso, University of Padova

Registration and Arrangements Chair: Harald Gossner, Infineon Technologies

Finance Chair: James W. Miller, Freescale

Seminar Chair: Horst Gieser, Fraunhofer IZM

Discussions Group Chair: Charvaka Duvvury, Texas Instruments

Special Interest Groups Chair: Markus Mergens, QPX

Posters Chair: Natarajan Mahadeva Iyer, GLOBALFOUNDRIES

Audio/Visual Chairs: Warren Anderson, AMD Guido Notermans, ST-Ericsson

US Publicity Chair: Robert Gauthier, IBM

Asia Publicity Chairs: Hiroyasu Ishisuka, Renesas Technology Natarajan Mahadeva Iyer, GLOBALFOUNDRIES

ESDA Board Advisor: Ginger Hansel, Dangelmayer Associates, LLC

Director of Operations: Lisa Pimpinella, ESD Association

Technical Program Committee:

Gianluca Boselli, Texas InstrumentsLorenzo Cerati, STMicroelectronicsMauro Ciappa, ETH ZürichDimitri Linten, IMEC Melanie Etherton, Freescale

Evan Grund, Grund Technical Solutions

Leo G. Henry, ESD & TLP ConsultantsHiroyasu Ishizuka, Renesas TechnologyGuillaume Jenicot, ON Semiconductor

Tim Maloney, IntelNicolas Nolhier, LAAS-CNRSDionyz Pogany, Technical University of Vienna

Wolfgang Stadler, Infineon TechnologiesTeruo Suzuki, FujitsuHoward Tang, UMCAugusto Tazzoli, University of PadovaVladislav Vashchenko, National SemiconductorAlbert Wallash, Hitachi GST Heinrich Wolf, Fraunhofer IZM

�

IEW

Abstract The SensiumTM is a complete wireless vital signs measurement mixed signal/RF system-on-chip platform. The primary objective is to provide clinicians with an affordable way to increase patient surveillance and safety by improving the accuracy and availability of patient vital signs data. Vital signs include respiration rate, heart rate, and skin temperature. In developing this personalized medical device, robust ESD performance was critical as the device can be deployed in a wide range of handling environments. This paper will present the key work on the combination of process and design choices made in the implementation of an ESD protection strategy for the entire chip and the subsequent qualification testing carried out in order to validate the robustness of the device.

Biography Paul Paddan graduated from the University of Warwick and worked for Plessey Research on CCD and MOS chips. He then co-founded a chip design company before joining Thomson CSF and then Austria Microsystems. Later he joined Parthus Ceva working on GPS RF technology before moving onto Toumaz Technology. Paul was the design and project manager for SensiumTM.

Design of an ESD Robust Wireless Sensor Chip for Medical ApplicationsPaul Paddan, Michael Best, Emelita Ferrer, Alan Chi Wai Wong, Derek Wood, Toumaz Technology; Helmut Buchner, and Harald Gossner, Infineon Technologies

Keynote

Invited Talk 1Future Challenges of ESD Protection – an Automotive OEM’s point of ViewChristian Lippert, Audi

Abstract With an increasing amount of electronics, the continuous improvement of vehicle reliability requires, as an essential part, significant enhancements in ESD-robustness. ESD events not only occur during packaging and handling, but also in the complete process chain from the semiconductor manufacturing up to OEM’s final assembly. The vehicle itself has to be ESD protected for different discharge conditions that occur in real life. Currently, each level of electronic development (microelectronics and electronic circuits) is using its own strategies in ESD protection. On the system level a large range of different ESD stress conditions, protection philosophies, and technical solutions is visible. To reach the next level in reliability we need to think about how to harmonize those different discrete ESD requirements. This paper will present a state-of-the-art automotive ESD protection and qualification strategy, the future challenges, and the necessary changes in mind to tackle them.

Biography Christian Lippert graduated in 2004 from Friedrich-Alexander-University of Erlangen-Nuremberg. He then joined the technical development division EMC of AUDI AG, responsible for EMC vehicle concepts and ESD.

IC Package Technology Advancements & Challenges for this DecadeMahadevan Iyer, Texas Instruments

Abstract During the last decade, IC package technology has taken a more prominent role, in parallel with the silicon technology scaling, addressing higher speed circuit performance, increased power dissipation, and system miniaturization. The ever increasing demands for cost effective miniaturized products with enhanced functionalities is bringing new challenges for packaging technologies. Chip–package design and modeling, electrical, thermal and thermo mechanical design optimizations, single chip and multi chip assembly and packaging technologies, new materials and processes, 3D integration method-ologies, and design for reliability, are the key packaging and integration challenges that are being addressed. This talk will address the packaging trends, challenges, and impact of these emerging packaging technologies on IC reliability.

Biography Dr. Iyer manages the Worldwide Semiconductor Packaging at Texas Instruments, Inc. He received his Ph.D for his thesis work on high speed interconnection technique for gigabit logic multi chip modules. Dr. Iyer has over 25 years of experience in semiconductor industry and academic centers and has worked with single chip and multi chip packaging technology design, assembly, and reliability. He has over 180 technical publications and 20 patents to his credit. He is a Senior member of IEEE and has been Technical Chair and Program Chair for various IEEE Packaging Technology Conferences.

Simulation Based Analysis of ESD Protection Elements on Systemlevel, Best Paper of ESD Forum 2009 Bastian Arndt, Continental Automotive

Abstract Comprehensive system level ESD protection design can be quite challenging, particularly when the protected module must meet both commonly enforced standards and special customer requirements. This talk presents an effective tool for optimization -- a simulation methodology of the whole electrical path involved during the ESD event from the source of stress to the integrated circuit at risk. It combines field simulation at the PCB level with compact simulation of relevant interconnect traces, passive, and active elements. This method, here demonstrated for an automotive ECU, can provide all the information necessary to tailor the external protection scheme and elements in order to meet multiple functional as well as robustness requirements.

Biography Bastian Arndt is a PhD student in EE at TU Dortmund working with Continental Automotive GmbH in the field of ESD protection for ECUs. For his work he received the Best Paper Award of the 2009 ESD Forum in Berlin.

Don’t miss this state of the art information!

Keynote Invited Talk 2

Invited Talk 3

�

IEWGet an overview of technology challenges!

ESD-Protection of Advanced RF and Broadband In-tegrated Circuits and MEMS Dimitri Linten, IMEC

Today’s RF applications reach higher operating frequencies than before, with a larger available bandwidth. Developing a successful ESD protection methodology for the RF IO pins requires both RF and ESD design skills. During the last decade, several RF ESD protection methodologies have been presented in literature. This seminar will classify the available techniques and present an overview on the state-of-the-art ESD solutions for both narrowband and wideband RF and mm-wave applications.

Additionally, in the recent year MEMS switching devices have been introduced into these applications. The study of the reliability and failure mechanisms of MEMS under ESD stress has therefore received increasing attention. Next to the ESD characterization of the MEMS, providing ESD solutions for ICs with integrated MEMS is currently a key challenge.

ESD-Aspects of FinFETs and other Most Advanced Devices Christian Russ, Infineon Technologies

The 28 nm and 22 nm CMOS technology nodes are already posing many ESD challenges on technology, device and circuit level. However, the main question still lies ahead of us: Will there be a fundamental change in device architecture to enable downscaling towards 16 nm? Planar bulk CMOS is still successfully pushing its own limits and the big disruption is still to come. But the race between classical CMOS bulk and novel 3-D device geometries such as FinFETs is already on! Obviously, ESD protection design must not be a show-stopper. Whatever the scenario will be – classical bulk CMOS or 3-D devices - we better get prepared!We give an overview on the ESD performance of IC technologies that are close to industrial production or which have good chances because of their proven ability for large scale integration. We compare advanced ESD devices in FinFET technology - on SOI and bulk substrate - with planar CMOS devices. We will assess process features introduced to push CMOS further, such as strained silicon or HighK dielectrics. Characterization data and failure mechanisms will help to judge voltage clamping, thermal properties, and turn-on speed of the devices, in view of their suitability for ESD protection, such as for hyper thin gate dielectrics and various voltages for supply or signaling.

CDM Charged Device Model Test: Current Status and Possible Alternatives Heinrich Wolf, Fraunhofer IZM

In a modern production environment the Charged Device Model (CDM) becomes more and more relevant concerning ESD failures of product ICs. Furthermore, the ESD design window is shrinking for modern ultra deep submicron technologies. This requires test methods with high accuracy and reproducibility. The current CDM standards allow for a high variation of the peak current value for a given pre-charge voltage. Mainly, the uncontrolled air discharge spark during a CDM stress introduces this lack in reproducibility and accuracy of the obtained failure thresholds. JEDEC and ESDA aim to merge their standards into one. Recently, new CDM-like test methods have been developed which should achieve more reliable test results. After a review of the current CDM status, including White Paper 2 of the Industry Council, this seminar will discuss and compare the different test methods.

ESD/EMC in an Automotive Environment Patrice Besse, Freescale

The ESD ruggedness is part of IC specifications and it is currently evaluated by well known stresses (CDM, MM, HBM). From a system point of view, the ESD robustness should guarantee safe operations if an ESD event appears while the product is functioning or not. For automotive, OEMs and car makers consider ESD an electromagnetic disturbance and it is usually part of a global electromagnetic compatibility (EMC) specification. IEC and ISO standards define the test procedures, but car makers also require specific ESD tests. For embedded system ESD and EMC, tests are achieved on cables and connectors of the Electronic Control Unit and a large part of the stress is withstood by the IC itself. ESD and EMC strategies have to be compatible at both the IC and system levels. As we will see on several products, external devices are often added to improve the ESD/EMC performances, but in some cases it does not help and can decrease the robustness. This seminar will discuss the common and specific ESD/EMC system requirements we need to take into account at the die level. An integrated ESD protection dedicated to the system level stresses will be presented as an example.

Seminars

Seminar Chair: Horst Gieser, Fraunhofer IZMThis group of seminars cover four closely connected topics. CDM and alternative characterization methods in the sub nanosecond regime are extremely helpful tools to analyze the protection capability in modern ICs. However, the results have to be carefully checked to avoid misinterpretation. To protect a system against malfunction during IEC discharge, very fast rising pulses with high energies need to be considered. EMC design methods largely determine how much the IC pin is affected. The implemented protection is often in competition with the performance requirements of a system, especially for RF and broadband interfaces. Meanwhile, methods are in place which provide a good solution for both high speed performance and ESD robustness. Finally, most modern communication systems are realized in very advanced CMOS technologies. This adds an additional challenge to ESD protection design and clearly limits the achievable robustness level of an on-chip protection for CDM like stress.

�

IEWChairman: Charvaka Duvvury, Texas InstrumentsDiscussion groups will occur on Tuesday and Wednesday evenings and are a very important part of the Workshop. Two very interesting discussion groups are offered each evening. Each discussion group is assigned a moderator who has extensive experience with the topic and will help to guide the discussion. However, the actual discussion flow will be at the discretion of those participating in each group. Everyone is encouraged to bring along data and ideas to share on topics that are of particular interest. As the Workshop approaches, please check the IEW web site for updates from the discussion group moderators.

The discussion group topics are as follows:

Discussion Groups

Open Poster SessionESD is a dynamic field and ideas don’t always wait for workshop or conference deadlines. If you have exciting new results that you want to share or even a problem that you would like to present to ESD experts, consider an open poster presentation. If you would like to bring an open poster to the workshop contact the poster chair at least one week before the workshop ([email protected]). He will provide you with instructions for the preparation of an open poster. All open posters are subject to review by the poster chair to ensure that the poster is appropriate and does not contain information of a sales/marketing rather than technical nature.

For more details on posters at the IEW, see the posters section of the IEW website: http://www.esda.org/IEW_poster.html

Discussion Group 1: Transient Latch-up: How to Test for It? How to Design for It? Moderator: Wolfgang Stadler, Infineon Technologies

Many talk about Transient Latch-up (TLU) but very little is done to address this in a systematic manner. Why is TLU important and what specifically is involved in it? Is TLU related to ESD system level tests? Is there any relationship to static JEDEC latch-up? When do we all agree for a standardized test? Can the IC be designed to be robust against TLU?

Discussion Group 2: ESD Qualification and ESD Control Methods Moderator: Reinhold Gaertner, Infineon Technologies

With the recent recommendations on reduction for ESD Target Levels, the focus on ESD control methods has become even more important. This discussion topic intends to address the ESD control methods in existence and what they mean for the new ESD qualification. The industry agrees that the measures to protect against HBM are well described in international standards. But what about CDM control? There is no specific description for this. Most of the measures are already intrinsically implemented, but if the current ESD levels are further reduced are there newer ESD controls that are needed? How should we properly inform and educate the supplier and the customer about ESD control?

Discussion Group 3: Automotive System ESD Protection Moderator: Markus Mergens, QPX

The automotive environment and the impact of ESD requirements are not always fully understood. This discussion topic intends to address these issues. Is there something special for the automotive environment? Are the ICs for automotive applications different from consumer ICs? Do they need higher component ESD? How do they tolerate a powered-up system upset due to ESD events? What other tests are important? Are these different from the IEC test?

Discussion Group 4: How Useful and Reliable are TLP Tools? Moderator: Leo G. Henry, ESD & TLP Consultants

Both the standard TLP and the Very Fast TLP are used to evaluate HBM and CDM performance respectively. In addition, now CCTLP is proposed for CDM. How good are these tools? Can we use them as back-up for false failures from the testers? What are their limitations? What should one watch out for? Will these tools ever replace actual testers?

Bring your expertise and join in the discussions!

�

IEWSpecial Interest Groups (SIG)

A special interest group (SIG) is a collaborative working team focused on one compelling topic of mutual interest. The SIG program at the IEW has been established to foster collaborative work on important ESD issues and we look forward to continued momentum throughout the year on these topics. The formation of SIGs is encouraged as a natural extension of the discussion group topics or any topic of interest to two or more attendees. Five SIGs are already scheduled for IEW 2010. Attendees are also encouraged to form new SIGs as they see fit. If you would like to form a new SIG please contact Markus Mergens at [email protected].

SIG Chair: Markus Mergens, QPX

SIG 1: Two-Pin HBM Testing New technology nodes are uncovering unwanted stresses from HBM tester parasitics and DUT-tester interactions that cause false failures. Today’s high performance modules have more pins than the largest HBM testers. The simplicity of 2-pin HBM testing offers solutions, but its speed is limited. This SIG will discuss HBM performance re-quirements and tradeoffs along with identifying the changes needed to the ESDA/JEDEC standards for 2-pin testing. Coordinators: Evan Grund, Grund Technical Solutions and Charvaka Duvvury, Texas Instruments

SIG 2: ESD Data Analysis Software On a regular basis, ESD engineers process and analyze measurement and/or simulation results from different test methods. They have to extract ESD parameters and manipulate functions over several de-vices. Spreadsheet programs are one common solution for this type of analysis despite not being designed for ESD data manipulation, which can make the work very tedious. Who should take the lead in the development of such tools: the ESD engineers and/or the ESD tester manufacturers? What are the requirements? Does each of us have his in-house optimized tool? Can we establish a common and open platform and build a user/developer community? At least two software tools will be presented and will be open for the ESD com-munity.Coordinators: Dimitri Linten, IMEC and David Tremouilles, LAAS-CNRS

SIG 3: System-level ESD Stress System-level ESD stress, being a concern for system designers for a long time, has now moved into the focus of on-chip ESD protec-tion development as well. Narrowing design windows, declines in achievable HBM and CDM robustness together with shorter system design cycles, demand a clear understanding of the specific require-ments of system ESD robustness at the IC design side and a better alignment between system, board, and IC design. This SIG will give an overview of the ongoing working group activities in this field and provides an informal platform for collecting recommendations and ideas for further work in these groups.Coordinator: Harald Gossner, Infineon Technologies

SIG 4: Transient Latchup (TLU)There is an ongoing discussion whether the Transient Latch-up stan-dard practice defined by the ESDA (ANSI/ESD SP5.4) really covers all “real world” TLU threats for current products. On the other hand it seems to be clear that transients are becoming increasingly impor-tant and there is no doubt that those transients can trigger latch-up. This SIG should collect input from industry experts to support and impact current standardization activities in this field. Coordinator: Wolfgang Stadler, Infineon Technologies

SIG 5: ESD EDA ToolsDo you have, use, or develop IC design automation and verification tools for ESD protection implementation? Whatever your answer is, our ESD EDA SIG is the place where you should be and share your needs, experience, or suggestions on ESD checks, tools, and meth-ods. We will continue the discussion and the work started in the pre-vious SIG meetings on this exciting topic. An update from the ESDA working group on ESD EDA will be given on the progress and status of the ESD EDA Technical Report. Your inputs will be very useful to the ESD community and customers!Coordinators: Michael Khazhinsky, Freescale and Vesselin Vassilev, Novorell

Work out your ESD issues in a collaborative team of high-level experts!

�

IEWMONDAY, MAY 10 Please have lunch before arriving at the facility; lunch will not be served on the first day.

Registration & Check-In1:00 p.m.- 6:00 p.m. Registration: Pick up badges and handouts 1:00 p.m.- 10:00 p.m. Room check-in: Get room assignment & room key

SEMINARS1:25 p.m. - 1:30 p.m. Seminar Welcome Horst Gieser, Seminar Chair

1:30 p.m. - 2:50 p.m. Seminar 1 - CDM and Alternatives Heinrich Wolf, Fraunhofer IZM

3:00 p.m. - 4:20 p.m. Seminar 2 - EMI/EMC Design Patrice Besse, Freescale

4:20 p.m. - 4:50 p.m. BREAK (Refreshments Provided)

4:50 p.m. - 6:10 p.m. Seminar 3 - RF ESD incl. MEMS Dimitri Linten, IMEC

6:30 p.m. - 8:00 p.m. DINNER (Dining Room)

8:00 p.m. - 9:20 p.m. Seminar 4 - ESD Aspects of FINFETs Christian Russ, Infineon Technologies

TUESDAY, MAY 117:00 a.m. - 8:00 a.m. BREAKFAST (Dining Room)

8:00 a.m. - 8:20 a.m. Welcome & Announcements

8:20 a.m. - 9:20 a.m. Invited Keynote: Design of an ESD Robust Wireless Sensor Chip for Medical Applications Paul Paddan, Toumaz Technology

POSTER SESSION 19:20 a.m. - 9:30 a.m. Poster Session 1 Introduction Natarajan Mahadeva Iyer, GLOBALFOUNDRIES

9:30 a.m. - 10:10 a.m. Poster Presentation Summaries

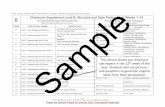

Poster 1.1 – Impact of Difference Between Discharge Meth-ods on CDM ESD Testing Y. Morishita, H. Ishizuka, T. Hiraoka, K. Hashimoto, N. Wakai, S. Kumashiro, MIRAI-Selete

Poster 1.2 – Negative Effects of Air Discharge Suppres-sion on Field- Induced CDM Test Repeatability David Eppes, Danielle Roth-Dunn, Mark Lapina, Warren Anderson, Advanced Micro Devices

Poster 1.3 – Exceptional First CDM Discharge Pulse Tilo Brodbeck, Reinhold Gaertner, Infineon Technologies

Poster 1.4 – Practical Approaches to CDM Test on High Speed and Large Package Devices Agha Jahanzeb, Charvaka Duvvury, Joe Schichl, James McGee, Texas Instruments, Inc.; John Fox, Texas Instruments Limited

Poster 1.5 – ESD Evaluation of 3D SIC Technology Using TSV S. Thijs, D. Linten, A. Mercha, G. Van der Plas, Y. Travaly, J. Van Olmen, IMEC; M. Scholz, IMEC and Vrije Universitei; G. Groeseneken, IMEC and Katholieke Universiteit Leuven

Poster 1.6 – Electrical Pulse Stressed Film Resistive Structures D. Bonfert, H. Wolf, H. Gieser, G. Klink, K. Bock, Fraunhofer Institute Reliability and Microintegration

Poster 1.7 – An Integrated Measurement Set-Up to Study the Impact of Atmosphere on ESD in MEMS Sandeep Sangameswaran, Guido Groeseneken, IMEC, ESAT, Katholieke Universiteit Leuven; Jeroen De Coster, Vladimir Cherman, Dimitri Linten, Steven Thijs, IMEC; Mirko Scholz, IMEC, Vrije Universiteit Brussels; Ingrid De Wolf, IMEC, MTM, Katholieke Universiteit Leuven

Poster 1.8 – Experimental Study of Gated Diode as ESD Protection in FDSOI High-k/Metal Gate 45 nm Node Technology Thomas Benoist, STMicroelectronics Crolles, CEA-Leti Minatec, IMEP-LAHC, Grenoble INP, Minatec; Claire Fenouillet-Beranger, Pierre Perreau, STMicroelectronics Crolles, CEA-Leti Minatec; Philippe Galy, Blaise Jaquier, STMicroelectronics; Christel Buj, Olivier Faynot, CEA-Leti Minatec; Pierre Gentil, IMEP-LAHC, Grenoble INP, Minatec

10:10 a.m. - 10:25 a.m. Group Picture

10:25 a.m. - 12:00 p.m. Poster Session 1 Refreshments provided

12:00 p.m. - 1:20 p.m. LUNCH (Dining Room)

TECHNICAL SESSION A - ON-CHIP PROTECTION DEVICES1:20 p.m.- 1:25 p.m. Announcements Gaudenzio Meneghesso, Technical Program Chair

1:25 p.m. - 1:50 p.m. Presentation A.1 – Insights into Breakdown of High-k/Metal Gate Stacks Under ESD Stress A. Ille, T. Pompl, C. Russ, H. Gossner, Infineon Technologies

1:50 p.m. - 2:15 p.m. Presentation A.2 – On the Interaction Between Substrate- Triggered ESD Protection Circuits and Embedded Parasitic Elements Gianluca Boselli, Texas Instruments

2:15 p.m. - 2:40 p.m. Presentation A.3 – On-Chip Protection of RF Pins Against HMM Discharges Guido Notermans, Dejan Maksimovic, Gerd Vermont, ST Ericsson, Zaventem Belgium; Michiel van Maasakkers, ST Ericsson, Nijmegen, The Netherlands; Fredrik Pusa, Catena Wireless Electronics; Theo Smedes, NXP Semiconductors

Schedule

�

IEWPOSTER SESSION 22:40 p.m. - 2:45 p.m. Poster Session 2 Introduction Natarajan Mahadeva Iyer, GLOBALFOUNDRIES

2:45 p.m. - 3:25 p.m. Poster Presentation Summaries

Poster 2.1 – Engineering Fully Silicided Large Output Driver For Maximum It1 H. Jiang, H. K. Yap, G.W. Zhang C. Wang, C. Cheng, P. R. Verma, J. Lim, M. I. Natarajan, GLOBALFOUNDRIES

Poster 2.2 – Self-Protection Capability of Integrated Power Arrays V.A. Vashchenko, D. LaFonteese, P. Hopper, National Semi-conductor Corporation; M. Scholz, D. Linten, S. Thijs, P. Jansen, G. Groeseneken, IMEC

Poster 2.3 – Dual-Direction Protection in Si-Ge BiCMOS Process V.A. Vashchenko, National Semiconductor Corporation

Poster 2.4 –Transient Characterization of High Voltage Switching Devices Under ESD Stress M. Scholz, G.Vandersteen, IMEC, Vrije Universiteit Brussels, Belgium; D. Linten, IMEC; S. Thijs, M. Sawada, HANWA Electronic; G. Groeseneken, IMEC, ESAT, Katholieke Universiteit Leuven

Poster 2.5 – Development and Qualification of ESD Protec-tion Demonstrators Using SCR Structure Compatible with Advanced CMOS Technologies Ph. Galy, C. Entringer, J. Bourgeat, F. Jezequel, B. Jacquier, A. Dray, STMicroelectronics

Poster 2.6 – Consideration of Design Window for ESD Power-Clamp in Next Generation Devices Hiroyasu Ishizuka, Yasuyuki Morishita, Takayuki Hiraoka, Kenji Hashimoto, Nobuyuki Wakai, Shigetaka Kumashiro, MIRAI-Selete Selete Sagamihara Of-fice, NEC Sagamihara Plant

Poster 2.7 – SCR-Based Power Supply Clamp for Low Leakage Applications Kiran Chatty, Michel J. Abou-Khalil, Robert Gauthier, Semiconductor Research and Development Center, IBM Systems and Technology Group; Nathaniel Peachey, Quek Chee, RFMD

Poster 2.8 – On-Chip ESD Protection with Improved High Holding Current SCR (HHISCR) Achieving IEC 8 kV Con-tact System Level Bart Sorgeloos, Ilse Backers, Olivier Marichal, Bart Keppens, Sofics

3:25 p.m. - 4:55 p.m. Poster Session 2 and Mixer Refreshments provided

5:00 p.m. - 6:00 p.m. Special Interest Groups (parallel sessions)

SIG1 Two-Pin HBM Testing: Evan Grund, Grund Technical Solutions; Charvaka Duvvury, Texas Instruments

SIG2 ESD Data Analysis Software: Dimitri Linten, IMEC; David Tremouilles, LAAS-CNRS

SIG3 System-Level ESD Stress: Harald Gossner, Infineon Technologies

6:30 p.m. - 8:30 p.m. CONFERENCE DINNER (business formal)

8:30 p.m. - 9:30 p.m. Discussion Groups (parallel sessions)

DG1 Transient Latch-up: How to Test for It? How to Design for It? Wolfgang Stadler, Infineon Technologies

DG2 ESD Qualification and ESD Control Methods: Reinhold Gaertner, Infineon Technologies

9:30 p.m. TALK AT THE FIRESIDE “Are Customers Really from Mars and the Suppliers from Venus? Find out From the 4-year Experience of the Industry Council”

WEDNESDAY, MAY 12 7:00 a.m. - 8:00 a.m. BREAKFAST (Dining Room)

8:00 a.m. - 8:10 a.m. Report on DG1 & DG2

8:10 a.m. - 8:15 a.m. Announcements

TECHnICAL SESSIOn B - SySTEM LEvEL ESD PROTECTIOn8:15 a.m. - 8:50 a.m. Invited Talk 1: Future Challenges of ESD Protection – an Automotive OEM’s Point of View Christian Lippert, Audi

8:50 a.m. - 9:15 a.m. Presentation B1 – Impact of a Decoupling Capacitance on ESD Propagation at System Level: Full Simulation and Measurement Comparison N. Monnereau, F. Caignet, D. Trémouilles, CNRS; LAAS, Université de Toulouse, UPS, INSA, INP, ISAE, LAAS

9:15 a.m. - 9:40 a.m. Presentation B2 – Designing the System Level ESD Protection Against IEC 61000-4-2 Stress with TLP Data and SPICE Simulation Lifang Lou, Charvaka Duvvury, Agha Jahanzeb, Texas Instruments

9:40 a.m. - 10:05 a.m. Presentation B3 – IC Characterization for ESD System: Is the Human Metal Model the Right Approach? Wolfgang Stadler, Tilo Brodbeck, Josef Niemesheim, Reinhold Gaertner, Harald Gossner, Werner Simbuerger, David Johnsson, Matthias Stecher, Yiqun Cao, Infineon Technologies

POSTER SESSION 310:05 a.m. - 10:10 a.m. Poster Session 3 Introduction Natarajan Mahadeva Iyer, GLOBALFOUNDRIES

10:10 a.m. - 10:45 a.m. Poster Presentation Summaries

Poster 3.1 – EDA Tool for Checking Signal Power Domain Crossings Melanie Etherton, Michael Khazhinsky, Edgar Oropeza, Eliseo Torres, Suzanne Biganzoli, Freescale Semiconductor; Steffen Lorenz, Louis Thiam, Cadence Design Systems

Schedule

�

IEWPoster 3.2 – Simple IC’s-Internal-Protection Models for System Level ESD Simulation D. Trémouilles, N. Monnereau, F. Caignet, M. Bafleur, CNRS; LAAS, Université de Toulouse; UPS, INSA, INP, ISAE; LAAS

Poster 3.3 – System to Component Level Correlation Factor S. Thijs, D. Linten, IMEC; M. Scholz, IMEC, Vrije Universiteit Brussels; C. Russ, W.Stadler, Infineon Technologies; M. Sawada, HANWA Electronics Ind. Co. Ltd.; G. Groeseneken, IMEC, Katholieke Universiteit Leuven

Poster 3.4 – A Case Study of System Level ESD Protection Agha Jahanzeb, Lifang Lou, Charvaka Duvvury, Scott Morrison, Texas Instruments

Poster 3.5 – Invasive System Level ESD Current Measurement Using Magnetic Field Probe Fabrice Caignet, Nicolas Monnereau, Nicolas Nolhier, LAAS-CNRS

Poster 3.6 – ESD/EOS Validation of Electrical Components Pasi Tamminen, NOKIA Corporation; Toni Viheriakoski, Cascade Metrology

Poster 3.7 – ESD Robustness verification for System-on-a-Chip Designs Pritesh Johari, Youlin Liao, Norman Chang, Aveek Sarkar, Apache Design Solutions

10:45 a.m. - 12:00 p.m. Poster Session 3 Refreshments provided

12:00 p.m. - 1:00 p.m. LUNCH (Dining Room)

1:00 p.m. - 5:30 p.m. FREE TIME - The afternoon is free for discussion or to enjoy outdoor recreation.

5:30 p.m. - 6:30 p.m. Special Interest Groups (parallel sessions)

SIG4 Transient Latch-up (TLU): Wolfgang Stadler, Infineon Technologies

SIG5 ESD EDA Tools: Michael Khazhinsky, Freescale, Vesselin Vassilev, Novorell

6:30 p.m. - 8:00 p.m. DINNER (Dining Room)

8:00 p.m. - 9:00 p.m. Discussion Groups (parallel sessions)

DG3 Automotive System ESD Protection: Markus Mergens, QPX

DG4 How Useful and Reliable are TLP Tools? Leo G. Henry, ESD & TLP Consultants

9:00 p.m. - 10:00 p.m. Open Poster Session

THURSDAY, MAY 13

7:00 a.m. - 8:00 a.m. BREAKFAST (Dining Room)

8:00 a.m. - 8:10 a.m. Report on DG3 & DG4

8:10 a.m. - 8:15 a.m. Announcements

TECHnICAL SESSIOn C&D - TRAnSIEnT BEHAvIOR AnD CDM EFFECTS8:15 a.m. - 9:00 a.m. Invited Talk 2 - IC Package Technology Advancements & Challenges for this Decade Mahadevan Iyer, Texas Instruments9:00 a.m. - 9:25 a.m. Presentation C.1– Impact of Voltage Overshoots on ESD Protection Effectiveness for High Voltage Applications Yiqun Cao, Infineon Technologies, Technische Univsität Dortmund; Ulrich Glaser, Alevtina Podgaynaya, Joost Willemen, Matthias Stecher, Infineon Technologies; Stephan Frei, Technische Universität Dortmund

9:25 a.m. - 9:50 a.m. Presentation C.2 – Cross Domain Protection Analysis and verification Using Whole Chip ESD Simulation Mototsugu Okushima, Tomohiro Kitayama, Susumu Kobayashi, Tetsuya Kato, Morihisa Hirata, NEC Electronics Corporation

9:50 a.m. - 10:15 a.m. Presentation C.3 – CDM2 – A New CDM Test Method for Improved Test Repeatability and Reproducibility Robert Given, Marcos Hernandez, Tom Meuse, Thermo Fisher Scientific

10:15 a.m. - 10:35 a.m. BREAK (Refreshments Provided)

10:35 a.m. - 11:00 a.m. Presentation D.1– Pulse Risetime Effect on Current Filamentary Modes and Interaction of Current Filaments in ESD Protection Devices W. Mamanee, S. Bychikhin, E. Gornik, D. Pogany, Vienna University of Technology; D. Johnsson, M. Stecher, H. Gossner, Infineon Technologies; P. Rodin, Ioffe Physicotechnical Institute

11:00 a.m. - 11:25 a.m. Presentation D.2– Influence of Geometrical Parameters on Time-to- Latch-Up of SCR-Based ESD Protection Structures Augusto Tazzoli, Gaudenzio Meneghesso, University of Padova; Martina Cordoni, Paolo Colombo, STMicroelectronics

11:25 a.m. - 11:50 a.m. Invited Talk 3 - Simulation Based Analysis of ESD Protection Elements on Systemlevel, Best Paper of ESD Forum 2009 Bastian Arndt, Continental Automotive

11:50 a.m. - 12:20 p.m. Special Interest Group Reports

12:20 p.m. - 12:25 p.m. IEW 2011 Announcement

12:25 p.m. - 12:40 p.m. Closing Remarks

12:40 p.m. - 1:30 p.m. LUNCH (Dining Room)

DEPART

Schedule

10

IEWARRIVAL AT EVANGELISCHE AKADEMIEMonday, May 10th: For those who are planning to attend the first tutorials, please plan to arrive after you have had your lunch. The Conference Center will not be prepared to serve you lunch. Registration will begin at 1:00 p.m.

TRANSPORTATIONTutzing, Germany is located about 40 km south of Munich at the western shore of Lake Starnberger See.

From Munich by RailFrom Munich International Airport take metro (S-Bahn) S1 or S8 to main station (Hauptbahnhof). Change trains there to S6 heading to Tutzing. Leave S6 at the final destination of Tutzing. It takes about 10 minutes to walk from Tutzing station to the Evangelische Akademie via Bahnhofstrasse, Hallberger Allee and Hauptstrasse to Schlossstrasse. Tickets for the S-Bahn can be bought at the information coun-ter of the airport in Terminal 1 next to the escalators to S-Bahn.It takes about 1 hour 30 minutes by train from the airport to Tutzing.Train schedules http://www.mvv-muenchen.de/en/home/index.htmlFrom Munich by CarExit the airport on motorway A92 heading Munich (München). At junction 4 München/Salzburg take A9 to Munich (München). At the end of the motorway (exit 76) turn right to ring road West (Mittlerer Ring West) following the signs to Garmisch-P. At junction to A95 enter motorway A95 in the direction of Garmisch-Partenkirchen. Take exit to Starnberg. In Starnberg take the B2 federal road towards Weilheim with destination Traubing. In Traubing you turn left and follow the signs guiding you to Tutzing.It takes about 1 hour 15 minutes by car from the airport to Tutzing.Car rental: http://www.munich-airport.de/en/consumer/anab/mietwagen/index.jspIEW ACCOMMODATIONSIEW attendees pay a package fee which covers the workshop registration, three days of lodging, and meals. Attendees are welcome to bring guests for an additional package fee covering the three days of lodging and meals. Please see the registration form for full details.The Evangelische Akademie Tutzing offers single and double guest rooms. Some of the rooms are located in the old castle wing and some located in the modern guest house. You can enjoy a wonderful view over Lake Starnberger See and the spacious park surrounding the building. All rooms offer private shower, WC and telephone. The arrangements in some of the guest rooms have been adjusted to the particular needs of handicapped guests.

● No reductions to the package fee will be made for partial stays or unused meals.● Smoking is permitted outdoors only.● Arrangements can be made for those with special dietary or physical requirements. Please send your requirements with the registration or

email to [email protected]● Plan to have lunch before you arrive at the Conference Center on Monday. A list of restaurants near the Academy can be found at

http://www.tutzing24.de/tourismus/branche.php?a=gastronomie

RESPONSIBILITIES OF ATTENDEESYou are expected to come prepared to participate actively in the discussions and meetings by sharing your experiences, concerns, questions, views, technical information, and test data, as appropriate. Your active involvement in the formal, as well as in the informal meetings and activi-ties, is the key ingredient for maximizing the value of the workshop for you and your fellow attendees. Enjoy IEW!In keeping with the relaxed and informal atmosphere of the workshop, we ask that attendees not overtly solicit, promote, or attempt to sell a commercial product or service at the workshop. On the other hand, we strongly encourage making business acquaintances and arranging meet-ings to be held after the workshop.

FOR YOUR VISITEarly May usually has nice weather with warm spring days. Warm clothing is recommended when walking in the evening since the nights can be a bit chilly. There are trails at the lake and in the surrounding hills. Sturdy shoes are useful for walking the surrounding areas on Wednesday afternoon. Except for the business-formal dinner on Tuesday night, comfortable, informal dress is encouraged during the conference.For information on things to do in the surrounding area visit http://esda.org/IEW_travel_accomodations.html

Travel Arrangements & AccommodationsWORKSHOP VENUE Evangelische Akademie • Schlossstrasse 2 • 82327 Tutzing Telefon: 08158 2510 Telefax: 08158 996444Internet: http://www.ev-akademie-tutzing.de

Advanced Registration Fees ESDA or IEEE Member $1,475 Non-ESDA or IEEE Member $1,575

The registration fee includes full workshop attendance and handout materials, seminar attendance, three nights’ lodging (Mon-Wed), nine meals (dinner Monday through lunch Thursday), as well as, morning and afternoon snacks and drinks.

Method of Payment

Credit Card (circle one) AMEX® Visa® MasterCard® Discover®

Card Number:

Exp. Date: Sec. Code:

Name on Card: Signature: Due to the limited space there are NO REFUNDS for attendee cancellations. (Guests are allowed to cancel up to 2 weeks prior to event start date for a 50% refund.)

Send this completed form and payment to: ESD Association, 7900 Turin Rd., Bldg. 3, Rome, NY 13440-2069

Phone: 315-339-6937 p Fax 315-339-6793 p [email protected] p www.esda.org

Workshop registration automatically includes a room reservation and provided meals.

Attendee:

Company:

Address:

City: State: Zip: Country:

Phone: ( ) E-mail: Fax: ( )

Please List Your Guests: Adults (Name) Children – under 3___ 3-12___ Guest fee is $550.00 each. Ages 3-12 are $300.00 each. Under 3 are free. Fee covers room and provided meals of workshop. No reductions will be made for shorter stays or unwanted meals.

Address is: (Please circle one) home or office Please check here if you do not wish to receive mail other than from ESDA Check if, under the Americans With Disabilities Act, you require any auxiliary aids or services.

Discussion GroupsI am interested in the following discussion group(s): Transient Latch-up: How to Test for It? How to Design for It? ESD Qualification and ESD Control Methods Automotive System ESD Protection How Useful and Reliable are TLP Tools?

Posters Will you be bringing a poster to the open poster session? Yes No If yes, what is the title of your poster? Special Interest Groups Would you like to form a new SIG? Yes No

If yes, what is the proposed topic for your group?

Special Interest GroupsI am interested in the following special interest group(s): 1: Two-Pin HBM Testing 2: ESD Data Analysis Software 3: System-level ESD Stress 4: Transient Latch-up (TLU) 5: ESD EDA Tools

Attendee $

Guests $

Total Enclosed $

Make checks payable to: ESD Association Purchase orders not accepted for registration

IEW

Check

Cost after March 29, 2010 ESDA or IEEE Member $1,875 Non-ESDA or IEEE Member $1,875

Only U.S. currency, checks drawn on a U.S. bank that is a member of the U.S. Federal Reserve will be accepted.

Please indicate any special dietary needs.: Arrival: Date Time • Departure: Date Time

1/��/�010

Students wishing to apply for reduced registration visit http://esda.org/IEW_registration.html. application deadline: March 29, 2010

International ESD Workshop Registration FormMay 10-13, 2010 Evangelische Akademie, Tutzing, Germany

Non-Profit Org.U.S. POSTAGE

PAIDPErmIT NO. 189

rOmE, NY

ESD Association7900 Turin road, Bldg. 3rome, NY 13440-2069

2010 IEW International Electrostatic Discharge Workshop

Evangelische Akademie May 10-13, Tutzing, Germany 2010 IEW HighlightsFour in-depth Seminars by Industry Leading Experts

Alternatives of CDM EMI/EMC Design RF ESD DesignESD-Aspects of FINFETs

Keynote PresentationDesign of an ESD Robust Wireless Sensor Chip for Medical Applications

Invited TalksFuture Challenges of ESD Protection – an Automotive OEM’s Point of ViewIC Package Technology Advancements & Challenges for this DecadeSimulation Based Analysis of ESD Protection Elements on Systemlevel

Twenty-four Technical Presentations and Posters Covering: Modeling and Simulation for ESD DesignNew Design Tools for ESDAdvanced Device PhenomenaOn-Chip ESD Protection DesignTest Methods and Tester EffectsSystem Level ESD Issues

Open Poster SessionDiscussion GroupsSpecial Interest Group (SIG) Meetings

Register early for discount prices!