06. Thumb Instructions

-

Upload

suhas-shirol -

Category

Documents

-

view

4 -

download

0

description

Transcript of 06. Thumb Instructions

-

ObjectivesTo understand 16-bit Thumb mode operation of ARM Processor.To understand the features of Thumb mode operation and how Thumb instructions decompress to ARM Mode.To know the technique of switching between ARM and Thumb mode of operations.To know the similarities and differences between ARM and Thumb mode of operationTo understand exception handling and branching in Thumb mode.To understand operation of data processing instructions and data transfer instructions in Thumb mode.

-

CPU Instruction Set ARM7TDMI processor has two instruction sets:the standard 32-bit ARM instruction seta 16-bit THUMB instruction set.

-

Processor Operating StatesARM state which executes 32-bit, word-aligned ARM instructions.

THUMB state which operates with 16-bit, halfword-aligned THUMB instructions.

-

Thumb Instruction SetARM architecture versions v4T and above define a 16-bit instruction set called the Thumb instruction set. The functionality of the Thumb instruction set is a subset of the functionality of the 32-bit ARM instruction set. A processor that is executing Thumb instructions is operating in Thumb state. A processor that is executing ARM instructions is operating in ARM state.

-

Thumb Instruction SetA processor in ARM state cannot execute Thumb instructions, and a processor in Thumb state cannot execute ARM instructions. You must ensure that the processor never receives instructions of the wrong instruction set for the current state.Each instruction set includes instructions to change processor state.

Note: ARM processors always start executing code in ARM state.

-

Thumb Instruction SetThe processor in Thumb mode uses same eight general-purpose integer registers that are available ARM mode.Some Thumb instructions also access the PC(ARM register 15),the Link Register(ARM register 14) and Stack Pointer(ARM register 13).When R15 is read,bit[0] is zero and bits[31:1]contain the PC.when R15 is written,bit[0] is IGNORED and bits[31:1] are written to the PC.Thumb does not provide direct access to the CPSR or any SPSR.Thumb execution is flagged by the T bit(bit[5]) in the CPSR.T==0 32-bit instructions are fetched(ARM instruction)T==1 16-bit instructions are fetched(Thumb instruction)

-

Thumb applicationsIn a typical embedded system:use ARM code in 32-bit on-chip memory for small speed- critical routinesuse Thumb code in 16-bit off-chip memory for large non-critical control routinesNote:Switching between ARM and Thumb States of Execution Using BX Instruction

-

Thumb applicationsFor Most Instruction Generated by the CompilerCondition Execution is not used.Source and Destination Registers are identicalOnly low registers usedConstants are limited sizeInline barrel shifter not used

-

DATA TYPESByte (8-bit): placed on any byte boundary.Half-word (16-bit): aligned to two-byte boundaries.Word (32-bit): aligned to four- byte boundaries.

-

FeaturesNot a complete architectureDynamically decompressed to ARM InstructionFully supported by ARM development toolsBoth entry and exit are done using corresponding BX Instruction

-

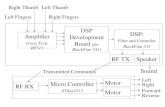

ARM7TDMI core

-

Mode SwitchingDefault entry to exception mode is always ARMExplicit entry to Thumb is done using ARM mode BX InstructionExplicit entry back to ARM mode is done using Thumb mode BX Instruction

-

Thumb Programmers ModelRegisters r0 to r7 are accessible (Lo)Few instructions require r8 to r15 to be specifiedr13 is used as the stack pointerr14 is used as the link registerr15 is used as the program counter

-

THUMB Register Organisation

-

ARM-Thumb SimilaritiesLoad-store architectureSupport 8-bit byte, 16-bit half-word and 32 bit word data types with aligned boundaries32 bit unsegmented memory.

-

ARM-Thumb differencesUnconditional Execution of instruction2-address format for data processingLess regular instruction formats.

-

Thumb exceptionWith exception processor is returned to ARM mode.

While returning previous mode is restored as SPSR is transferred to CPSR

-

Thumb BranchingShort conditional branches

Medium range unconditional branches

Long range Subroutine calls

Branch to change to ARM Mode

-

Branch Instruction FormatsB B BL BX Rm1514131211870

1 1 0 1Condition8-Bit Offset

1 1 1 0 011 Bit Offset

1 1 1 H11 Bit Offset

0 1 0 0 0 1 1 1 0HRm0 0 0

-

FeaturesDifferent format for each caseOffset is reduced to 11bit and 8 bitOffset is shifted left by 1-bit (to give half-word alignment) and sign-extended to 32 bits.BL is more subtle to give 22-bit offset using link register for temporary storageNo direct mapping to ARM instructions as Thumb require half-word aligned offsets.

-

BL InstructionTo allow for a reasonably large offset to the target subroutine each of these two instructions is automatically translated by the assembler into a sequence of two 16 bit thumb instructionsH = 10LR := PC + (sign-extended offset shifted left 12 places);

H = 11PC := LR + (offset shifted left 1 place)

LR := address of next instruction

-

Software Interrupt InstructionAddress of next instruction is saved in r14_svcCPSR is saved in r14_svcDisables IRQ, Clears T bit, Enters Supervisor modePC is forced to 0x088 bit immediate is zero extended to fill the 24-bit field in the ARM instruction.Limits SWIs to first 256 of 16 million ARM SWIs.

1 1 0 1 1 1 1 18 Bit Immediate

-

Data ProcessingFairly complex instruction formatsNo conditional executionSeparate shift operations provided, no shifting of second operandAll data processing instruction set condition code bits (no need of S)

-

Instruction formats Rd, Rn, Rm Rd, Rn, # Rd|Rn, Rm|Rs Rd, Rn, # Rd, #

-

InstructionsMOV Rd, #MVN Rd, RmCMP Rn, #CMP Rn, RmCMN Rn, RmTST Rn, Rm

-

InstructionADD Rd, Rn, #ADD Rd, #< imm8>ADD Rd, Rn, RmADC Rd, RmSUB Rd, Rn, #SUB Rd, #< imm8>SUB Rd, Rn, RmSBC Rd, RmNEG Rd, Rn

-

InstructionLSL Rd, Rm, #LSL Rd, RsLSR Rd, Rm, #LSR Rd, RsASR Rd, Rm, #ASR Rd, RsROR Rd, Rs

-

InstructionAND Rd, RmEOR Rd, RmORR Rd, RmBIC Rd, RmMUL Rd, Rm

-

Instruction (using Hi registers)ADD Rd, Rm(1 or 2 Hi registers)CMP Rn, Rm(1 or 2 Hi registers)MOV Rd, Rm(1 or 2 Hi registers)ADD Rd, PC, #ADD Rd, SP, #ADD SP, SP, #SUB SP, SP, #Except others donot set condition code bits

-

Data Transfer InstructionLDR|STR Rd, [Rn, #off5]LDR|STR Rd, [Rn, Rm]LDRB|STRB Rd, [Rn, #off5]LDRB|STRB Rd, [Rn, Rm]LDRH|STRH Rd, [Rn, #off5]LDRH|STRH Rd, [Rn, Rm]Signed operands:LDR|STR {S} {H|B} Rd, [Rn, Rm]

-

Multiple register transfersLDMIA|STMIA Rn!, { }

Rn may be any register among Ro R7

Register set can be any subset of R0 R7 but not base register Rn

Write back to base register is always selected.

-

Stack ModePOP|PUSH { {, R}}

R13 (sp) is used as base register

Uses Full Descending Stack

In addition any subset of Ro-R7 registers LR (lr) may be included in PUSH instruction and PC (pc)may be included in POP instruction

-

Thumb-ARM DecompressionTranslation from 16-bit Thumb instruction to 32-bit ARM instructionCondition bits changed to alwaysLookup to translate major and minor opcodesZero extending 3-bit register specifiers to give 4-bit specifiersZero extending immediate valuesImplicit S(affecting condition codes) should be explicitly specified.Thumb 2-address format must be mapped to ARM 3-address format

-

PropertiesThumb code requires 70% of space of ARM codeThumb code uses 40% more instructions than the ARM codeWith 32-bit memory ARM code is 40% fasterWith 16-bit memory Thumb code is 45% faster than ARM codeThumb code uses 30% less external memory power than ARM code.

-

SummaryThumb ARM mode switchingSimilarities and differencesThumb exception handlingData processing instructionsData transfer instructionsSeparate shift instructionsRestricted stack operations.

-

Thank You, Any Questions ?