© 2005 Altera Corporation DSP Builder v5.1.0 October 2005.

-

Upload

winifred-reynolds -

Category

Documents

-

view

224 -

download

3

Transcript of © 2005 Altera Corporation DSP Builder v5.1.0 October 2005.

© 2005 Altera Corporation

DSP Builder v5.1.0DSP Builder v5.1.0

October 2005October 2005

2

© 2005 Altera Corporation - Confidential

PrerequisitesPrerequisites

Understanding of DSP Builder Understanding of Simulink Understanding of SOPC Builder and

Avalon Interface Specification Understanding of IP MegaCore Design

Flow Understanding of Quartus II

3

© 2005 Altera Corporation - Confidential

AgendaAgenda

DSP Builder Overview New Features in DSP Builder v5.1.0 Enhancements Known Issues Conclusion

© 2005 Altera Corporation

OverviewOverview

5

© 2005 Altera Corporation - Confidential

System Level Simulation of Algorithm Model

MATLAB/Simulink

System Level Simulation of Algorithm Model

MATLAB/Simulink

System Level Verification of Hardware Implementation

Hardware

System Level Verification of Hardware Implementation

Hardware

RTL ImplementationRTL Simulation

Leonardo SpectrumPrecision, Synplify

Quartus II, ModelSim

RTL ImplementationRTL Simulation

Leonardo SpectrumPrecision, Synplify

Quartus II, ModelSim

System Level Design ToolSystem Level Design Tool

Single Simulink RepresentationSingle Simulink RepresentationSystem-level

Verification

Synthesis, Place ‘n Route, RTL Simulation

Algorithm

Modeling

Development Development Implementation Implementation VerificationVerification

System Algorithm Design and FPGA Design Integrated

6

© 2005 Altera Corporation - Confidential

Verify in Hardware

Place and Route

HDL Synthesis

Creates Simulation Testbench

DSP Builder OverviewCreates HDL Code

Creates SOPC Builder Ready Component

Download Design to DSP Development Kits

7

© 2005 Altera Corporation - Confidential

Version CompatibilityVersion CompatibilityDSP Builder

MATLAB/

Simulink*Notes

5.0.0 R13, R14,

R14SP1, R14SP2

Recommends Quartus II v5.0

5.0.1 R13, R14,

R14SP1, R14SP2

Recommends Quartus II v5.0

5.1.0 R14,R14SP1, R14SP2, R14SP3

Recommends Quartus II v5.1

Note (*) Note (*) MATLAB/Simulink R13: Matlab v6.5, Simulink v5.0MATLAB/Simulink R13: Matlab v6.5, Simulink v5.0 MATLAB/Simulink R14: Matlab v7.0, Simulink v6.0MATLAB/Simulink R14: Matlab v7.0, Simulink v6.0 MATLAB/Simulink R14SP1: Matlab v7.0.1, Simulink v6.1MATLAB/Simulink R14SP1: Matlab v7.0.1, Simulink v6.1 MATLAB/Simulink R14SP2: Matlab v7.0.4, Simulink v6.2MATLAB/Simulink R14SP2: Matlab v7.0.4, Simulink v6.2 MATLAB/Simulink R14SP3: Matlab v7.1, Simulink v6.3MATLAB/Simulink R14SP3: Matlab v7.1, Simulink v6.3

© 2005 Altera Corporation

New FeaturesNew Features

9

© 2005 Altera Corporation - Confidential

DSP Builder v5.1 New FeaturesDSP Builder v5.1 New Features

HDL Import Enhanced SOPC Builder Integration Support Multiple Versions of IP MegaCores Bit Width Parameterization Name Propagation

© 2005 Altera Corporation

HDL ImportHDL Import

11

© 2005 Altera Corporation - Confidential

HDL ImportHDL Import Import VHDL, Verilog

or Quartus II Project Simulink Simulation

Model is Automatically Generated

Allows Co-Simulation Does Not Require 3rd

Party Simulator

Allow Multiple Instantiations

12

© 2005 Altera Corporation - Confidential

HDL Import InterfaceHDL Import Interface Supports Hierarchical

Designs with Multiple Entities Add Verilog/VHDL Files or

Select Quartus II Project Set Top-Level Entity (Verilog

or VHDL only) Compile

Generate Simulink Model

13

© 2005 Altera Corporation - Confidential

HDL Import RequirementsHDL Import Requirements Single Clock Domain Synchronous Design Supports Generic Memory and Logic Functions

Logic Elements Memory DSP Blocks

Does Not Support Device Specific Functions Examples - PLL, LVDS, WYSIWYG

Refer to DSP Builder Reference Manual for Complete List of Supported MegaFunctions

14

© 2005 Altera Corporation - Confidential

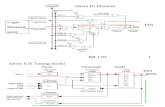

Design Flow using HDL ImportDesign Flow using HDL Import

15

© 2005 Altera Corporation - Confidential

What About SubSystemBuilder?What About SubSystemBuilder? Import HDL File User Creates Own

Simulation Model Speed Up Simulation

Using Own Simulink Model

Can Use SubSystemBuilder If Design Contains Unsupported LPMs/MegaFunctions

16

© 2005 Altera Corporation - Confidential

Comparison of HDL Co-Design FeaturesComparison of HDL Co-Design Features

Features Design Effort Simulation Speed

HDL Import Low Average

SubSystem Builder High Note(1)

Hardware in the Loop (HIL)

Medium Fastest

Link for ModelSim Medium Fast

Note: (1) User creates their own Simulink simulation model. Simulation speed depends on the type of simulation model.

© 2005 Altera Corporation

Enhanced SOPC Builder Integration

Enhanced SOPC Builder Integration

18

© 2005 Altera Corporation - Confidential

SOPC Builder IntegrationSOPC Builder Integration User Can Build Any Avalon SOPC Component

Dragging and Dropping Avalon Interfaces into DSP Builder Design Validate by Simulating in Simulink Export to SOPC Builder by Generating HDL and PTF from Signal

Compiler

19

© 2005 Altera Corporation - Confidential

Enhanced SOPC Builder IntegrationEnhanced SOPC Builder Integration

Interface Blocks Avalon Slave Avalon Master

Wrapped Blocks Avalon Read FIFO Avalon Write FIFO

Multiple Slaves and Masters

Advanced Avalon Bus Support

20

© 2005 Altera Corporation - Confidential

Interface BlocksInterface Blocks Low-level Access to

Avalon Signals All Ports have “Pass-

Through” Behaviour

Allows Multiple Slaves/Masters

Mechanism for setting PTF variables

Dialog to Configure Mode of Operation

Avalon Slave Avalon Master

21

© 2005 Altera Corporation - Confidential

Avalon MasterAvalon Master User Configurable to

Allow Subset of Signals

Modes of Operation Flow Control Pipeline Transfers Burst Transfers

22

© 2005 Altera Corporation - Confidential

Avalon Master SignalsAvalon Master Signals

Signal Type SignalsFundamental clk, waitrequest, address, read,

readdata, write, writedata, byteenable

Pipeline readdatavalid, flush

Burst burstcount

Flow Control endofpacket

Other irq, irqnumber

23

© 2005 Altera Corporation - Confidential

Avalon Master ExampleAvalon Master ExampleInput

Output

24

© 2005 Altera Corporation - Confidential

Avalon SlaveAvalon Slave User Configurable to

Allow Subset of Signals

Modes of Operation Flow Control Pipeline Transfers Burst Transfers

25

© 2005 Altera Corporation - Confidential

Avalon Slave SignalsAvalon Slave Signals

Signal Type SignalsFundamental clk, address, read, readdata, write,

writedata, byteenable

Wait-State waitrequest

Pipeline readdatavalid

Burst burstcount, beginbursttransfer

Flow Control readyfordata, dataavailable, endofpacket

Other irq

26

© 2005 Altera Corporation - Confidential

Avalon Slave ExampleAvalon Slave ExampleInput

Output

27

© 2005 Altera Corporation - Confidential

Wrapped BlocksWrapped Blocks Higher Level of

Abstraction Map Avalon Signals to

a “Standard” Subset Both Read/Write

FIFOs Handle Streaming Data Test Avalon Interface

in Simulink Environment

Avalon Write FIFO

Avalon Read FIFO

28

© 2005 Altera Corporation - Confidential

Avalon Write FIFOAvalon Write FIFO Hierarchical

Component Configuration Dialog

Data Type Data Width FIFO Depth

29

© 2005 Altera Corporation - Confidential

Avalon Write FIFO InternalsAvalon Write FIFO Internals Look Under Mask

User Can Customize Functionality using Mask Editor

30

© 2005 Altera Corporation - Confidential

Avalon Write FIFO SignalsAvalon Write FIFO Signals

Signal DescriptionTestData Pass through simulation data to DataOut one

cycle after Ready is asserted

Stall Simulate stall conditions, and may cause underflow to SOPC component. When asserted, data provided by TestData is cached and no Avalon writes take place.

Ready When asserted, indicates downstream hardware is ready for data.

DataOut Output from FIFO

DataValid Asserted when valid output is presented on DataOut

31

© 2005 Altera Corporation - Confidential

Avalon Read FIFOAvalon Read FIFO Hierarchical

Component Configuration Dialog

Data Type Data Width FIFO Depth

32

© 2005 Altera Corporation - Confidential

Avalon Read FIFO InternalsAvalon Read FIFO Internals Look Under Mask

User Can Customize Functionality using Mask Editor

33

© 2005 Altera Corporation - Confidential

Avalon Read FIFO SignalsAvalon Read FIFO Signals

Signal DescriptionStall Simulate stall conditions, applying backpressure

to the SOPC Component. When asserted, data provided on Data fills up FIFO but no Avalon reads take place.

Data Outgoing data from user’s design

DataValid Asserted when valid signal is presented on Data

TestDataOut Output from FIFO over Avalon Interface

TestDataValid Asserted when valid output is presented on TestDataOut

Ready When asserted, indicates slave is ready to receive data.

34

© 2005 Altera Corporation - Confidential

Testing BlocksTesting Blocks

Streaming Avalon Converter Provides Data to Avalon Write FIFO Collects Data from Avalon Read FIFO

Not Synthesizable

35

© 2005 Altera Corporation - Confidential

Avalon Write/Read FIFO ExampleAvalon Write/Read FIFO Example

36

© 2005 Altera Corporation - Confidential

Simulink SimulationSimulink Simulation

Avalon Blocks Accept Simulink Data Use Standard Simulink Source/Sink Blocks

37

© 2005 Altera Corporation - Confidential

HDL and PTF GenerationHDL and PTF Generation Set Option to

Generate PTF in Signal Compiler

VHDL Entity/Port Names Derived From Block

PTF File Automatically Generated Needed for Import in

SOPC Builder Component Appears in

SOPC Suite

38

© 2005 Altera Corporation - Confidential

SOPC Builder System EditorSOPC Builder System Editor

Nios II

H/WCore

+ DMAs

39

© 2005 Altera Corporation - Confidential

What About Avalon Ports?What About Avalon Ports? Only For Legacy

Design Allow One Slave Per

Design Avalon Slave Block

Has Same Functionality Except for Chip Select

© 2005 Altera Corporation

Other New FeaturesOther New Features

41

© 2005 Altera Corporation - Confidential

IP MegaCore SupportIP MegaCore Support Access to Multiple Versions

of IP Versioned MegaCore

Blue Color Recommended for New

Designs Legacy MegaCore

Gray Color For Backwards Compatibility Warnings Will Be GeneratedExample:

Warning: The block ‘test/csc' is linked to 'MegaCoreAltr/csc', which is a legacy block in the library and should not be used in new designs.

42

© 2005 Altera Corporation - Confidential

Update IP MegaCoreUpdate IP MegaCore

Automatic Update Global Update Create Two Variables in MATLAB

dspbuilder_reinstall_megacores = ‘on’dspbuilder_auto_update_megacore=‘on’

Rerun setup_dspbuilder Update MDL (Edit Menu) or Ctrl-D

Manual Update Design Specific Update update_megacores [design_name]

43

© 2005 Altera Corporation - Confidential

Design Parameterization SupportDesign Parameterization Support

User can explore design optimization possibilities

5.0 5.1

44

© 2005 Altera Corporation - Confidential

Propagation of Signal NamesPropagation of Signal Names

© 2005 Altera Corporation

EnhancementsEnhancements

46

© 2005 Altera Corporation - Confidential

DSP Builder v5.1 EnhancementsDSP Builder v5.1 Enhancements

Error Message Improvements Simulation Performance Enhancements Documentation Improvements

47

© 2005 Altera Corporation - Confidential

Improved Error Messaging

Blocks causing error are highlighted

Hyperlinks in MATLAB command window

48

© 2005 Altera Corporation - Confidential

IP SimulationIP Simulation

Simulation Time Speed Up Typically ~20% Faster

Improved Memory Usage Previously Memory Grew Linearly During

Simulation, Limiting Simulation Time Less Variation in Simulation Time

Previously > 2x Difference in Run-Time Possible for Identical Simulations

Now Always Minimum

49

© 2005 Altera Corporation - Confidential

Documentation ImprovementsDocumentation Improvements

Integrated with Matlab help

© 2005 Altera Corporation

Known IssuesKnown Issues

51

© 2005 Altera Corporation - Confidential

HIL and HDL Import Using SBFHIL and HDL Import Using SBF

Simulation Mismatch Using HIL or HDL Import Block with Signed Binary Fractional (SBF) Format

Convert SBF to Signed Using Binary Point Casting Blocks

SPR#189659

52

© 2005 Altera Corporation - Confidential

Unique Entity NamesUnique Entity Names

Option to Generate Unique Hierarchical Names Cannot be Easily Unset

Option is Disabled by Default To Enable:

dspbuilder_enable_unique_hierarchy_name = true;

SPR#189491

53

© 2005 Altera Corporation - Confidential

SignalCompiler Flow ShortcutSignalCompiler Flow Shortcut

Shortcut for “Execute steps 1, 2 and 3” Fails for 3rd Party Synthesis Tools

Run Steps Separately SPR#190351

© 2005 Altera Corporation

ConclusionConclusion

55

© 2005 Altera Corporation - Confidential

ConclusionConclusion

DSP Builder Offers a Complete Integrated Platform with Seamless Flow From System Design to Hardware Design

HDL Import Allows HDL Co-Design Enhanced SOPC Builder Integration Simulation Speed Improvements Improved Usability

© 2005 Altera Corporation

Back-up SlidesBack-up Slides

57

© 2005 Altera Corporation - Confidential

ReferencesReferences

AN402: Black-Boxing in DSP Builder AN403: Avalon Master/Slave Blocks in

DSP Builder DSP Builder Reference Manual DSP Builder User Guide DSP Builder Release Notes DSP Builder Errata Sheet

58

© 2005 Altera Corporation - Confidential

DSP Builder TrainingDSP Builder Training

Previous Training Material on DSP Builder Molson

MAT https://go.altera.com/extranet2001/education/internal_training/pr

esentations/int-presentations.html AppsNet

https://go.altera.com/extranet2001/support/iAPPS/specialty_support/ip/dsp/app-spec_ip_dsp.html#dspBuilder

DSP Technology Symposium https://go.altera.com/extranet2001/education/internal_training/int

ernal_tech_training/int-presentations/edu-int_tech_presentations.html\

59

© 2005 Altera Corporation - Confidential

DSP Builder Roadmap DSP Builder Roadmap

Q3

DSP Builder 5.1

HDL Import

Simulation Speed Improvements

Enhanced SOPC Builder Integration

Q4

2005

Q1 Q2 Q3 Q4

2006

DSP Builder 6.0

Multi-channel management blocks

External Memory Support

SOPC Datapath Integration

DSP Builder 6.1

Fixed-point data type

Frame-based simulation

HIL Improvements

60

© 2005 Altera Corporation - Confidential

Competitive AnalysisCompetitive Analysis

+ = Pro= NeutralN/A = Not Available

Features DSP Builderv5.1.0

System GeneratorV7.1.0

RTL Import + Co-Processor Strategy + Hardware Co-

Simulation +

HDL Co-Simulation Synthesis User

Interface+

61

© 2005 Altera Corporation - Confidential

Hardware in the Loop (HIL)Hardware in the Loop (HIL)

Simulation Acceleration Instrumentation Simple Hardware Interface

JTAG Connector

SinkSource

62

© 2005 Altera Corporation - Confidential

HIL Design FlowHIL Design Flow Step 1 : HIL Block Configuration Step 2 : Quartus II Compilation, SOF Program Step 3 : Simulate

JTAG HDLWrapper

Configure Compile/Program Simulate

63

© 2005 Altera Corporation - Confidential

Co-simulate HDL using ModelSimCo-simulate HDL using ModelSim

Bidirectional Link Between MATLAB/Simulink and ModelSim

Provided by Mathworks

Link to ModelSimLink to ModelSim ModelsimModelsimMATLABMATLABSimulinkSimulink

System-Level DesignSystem-Level Designand Simulationand Simulation

Co-simulation andCo-simulation andVerificationVerification HDL SimulationHDL Simulation

64

© 2005 Altera Corporation - Confidential

Link to ModelSim Design FlowLink to ModelSim Design Flow Step 1 : Insert HDL into Simulink as Black-Box Step 2 : Configure VHDL Co-Simulation Block Step 3 : Set Up ModelSim and Load Model Step 4 : Start Simulation in Simulink

Configure Set Up ModelSim Simulate

65

© 2005 Altera Corporation - Confidential

Subsystem BuilderSubsystem Builder Import HDL Design and Black-Box Creates Simulink Symbol of Subsystem User Creates Simulation Model

66

© 2005 Altera Corporation - Confidential

DSP Builder Path in MATLAB DSP Builder Path in MATLAB

Install Path Not Removed During Un-installation of DSP Builder v5.0

Conflict Due to Multiple Paths to Library Edit startup.m MATLAB Script to Comment

Out Path <MATLAB install dir>\toolbox\local\startup.m %path(path,'C:\altera\DSPBuilder\AltLib');